### REGULARITIES OF POWER CONSUMPTION IN QUASIADIABATIC LOGIC GATES

(supervisor: Vladimir Losev) Evgeny Sidelnikov

## OUTLINE

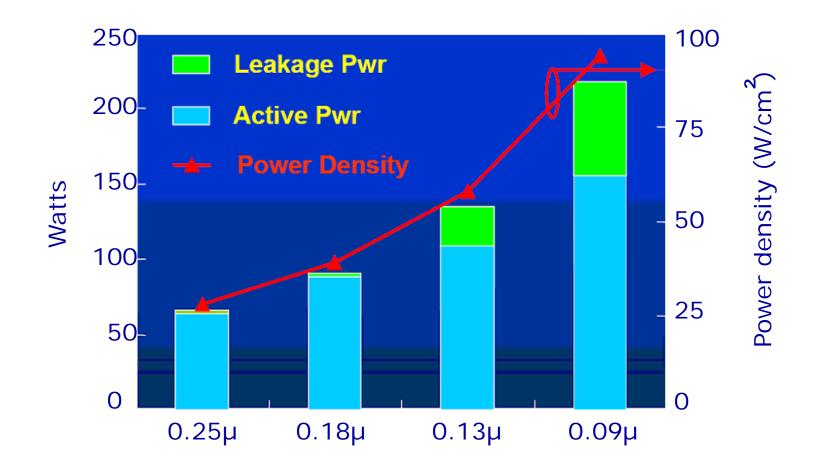

- \* POWER DENSITY TREND

- \* TRADTIONAL WAY TO REDUCE POWER CONSUMPTION

- \* ACTIVE POWER REDUCTION

- \* PERSPICTIVE VARIANTS OF ADIABATIC STATIC LOGIC

- \* QUASIADIABATIC STATIC LOGIC GATES FEATURES

- \* PERSPECTIVE VARIANTS OF ADIABATIC DYNAMIC LOGIC

- \* RESULTS OF SIMULATION

POWER DENSITY TREND

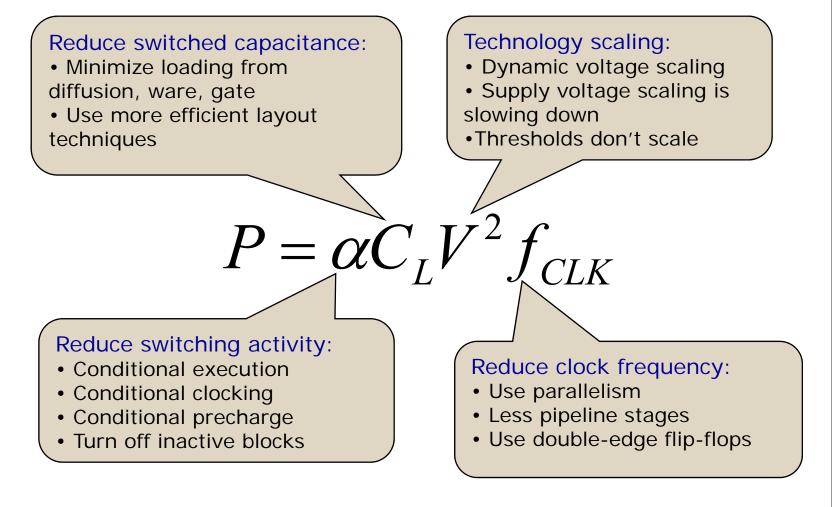

#### TRADTIONAL WAY TO REDUCE POWER CONSUMPTION

$P_{\text{avg}} = P_{\text{switching}} + P_{\text{short-circuit}} + P_{\text{leakage}} = \alpha_{0->1} C_{\text{L}} \bullet V_{\text{dd}}^2 \bullet f_{\text{clk}} + I_{\text{sc}} \bullet V_{\text{dd}} + I_{\text{leakage}} \bullet V_{\text{dd}}$

| Algoritmical                     | Logical             | Circuits topology                                                                                   | Technology process                              |  |

|----------------------------------|---------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------|--|

| Reduce<br>operation<br>per cycle | Boolean<br>function | Type of circuits<br>topology<br>Dynamic logic<br>Static logic,<br>Clock gating<br>Sleep transistors | Leakage<br>(Isolation,SOI)<br>Threshold voltage |  |

| Reduce<br>switching<br>activity  | Logical basis       | MOS, CMOS, BJT,<br>BiCMOS, SiGe                                                                     | Subthreshold<br>current,<br>Tunneling           |  |

#### ACTIVE POWER REDUCTION

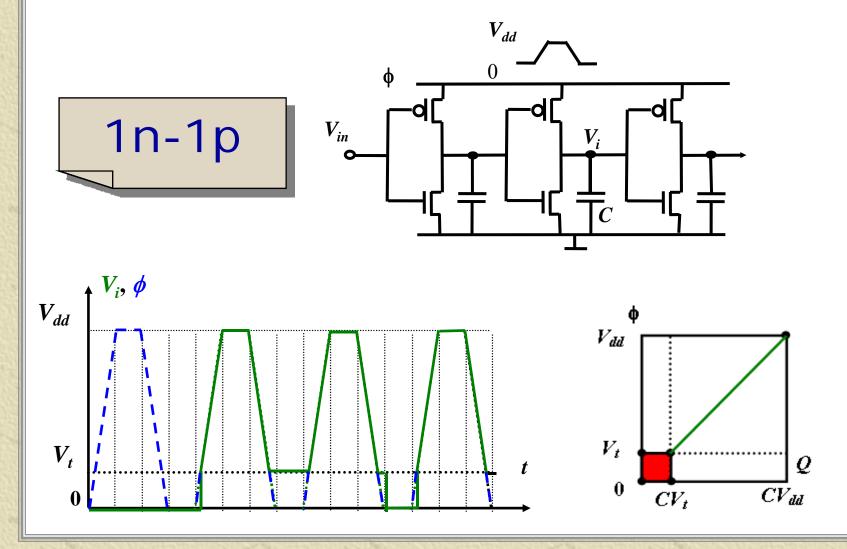

#### PERSPICTIVE VARIANTS OF ADIABATIC STATIC LOGIC

#### PERSPICTIVE VARIANTS OF ADIABATIC STATIC LOGIC

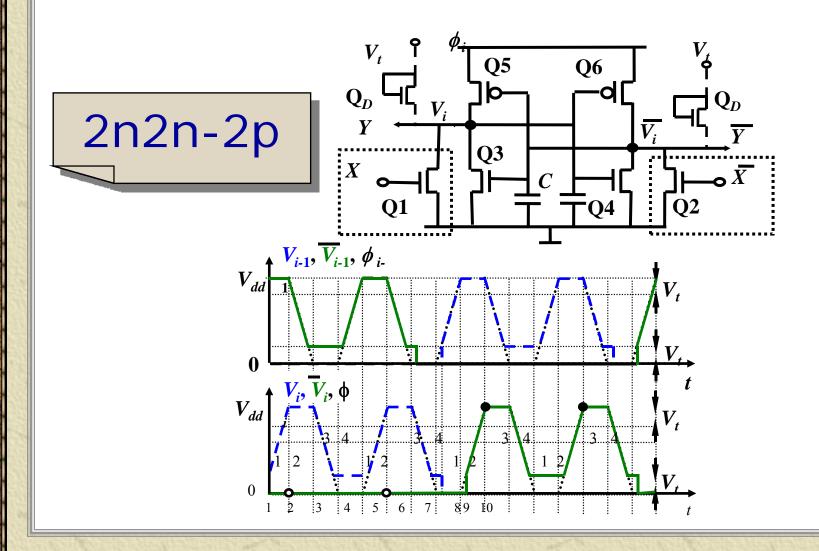

#### *QUASIADIABATIC STATIC LOGIC GATES FEATURES*

| Main features               | CMOS | 1n1p | 2n-2n2p |

|-----------------------------|------|------|---------|

| Degree of adiabatic         | 0    | 2    | 2       |

| pipeline                    | No   | No   | Yes     |

| Reliability                 | Yes  | Yes  | No      |

| Inverse signal processing   | No   | No   | Yes     |

| MOS q-ty in N input gates   | 2N   | 2N   | 2N+4    |

| Q-ty of power supply phases | 0    | 1    | 4       |

| Q-ty of power rails         | 2    | 2    | 5       |

| Other req.                  |      |      | _       |

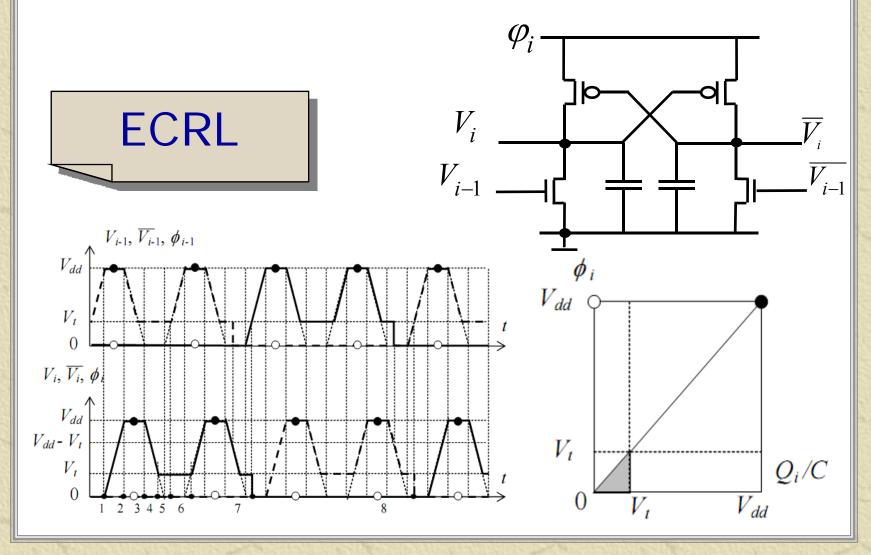

#### PERSPECTIVE VARIANTS OF ADIABATIC DYNAMIC LOGIC

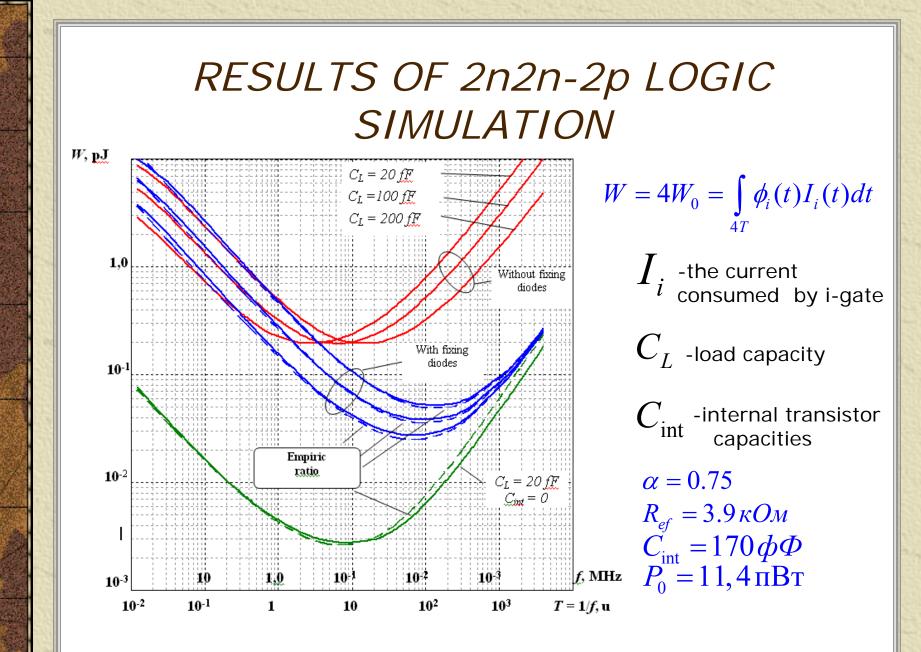

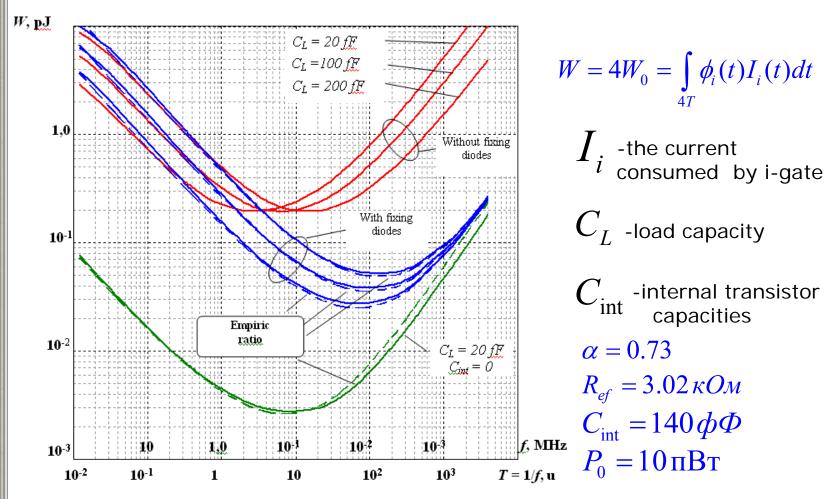

#### RESULTS OF ECRL LOGIC SIMULATION

\_\_\_\_\_

## CONCLUSION

\* The established laws allow to choose the compromise between power consumption and speed, optimize power characteristics of base gates.

It's also allowed to predict their improvement at quality of technology

# THANK YOU!