Moscow Institute of Electronic Technology (Technical University)

# Research of integrated digital decimation filters

Zhukov Dmitry

## INTRODUCTION

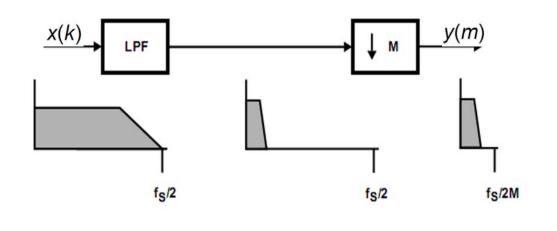

In digital signal processing, decimation is technique for reducing the number of samples in a discrete-time signal.

Decimation is a two-step process:

- Low-pass anti-aliasing filter

- Downsampling

Predictable Success

Predictable Success

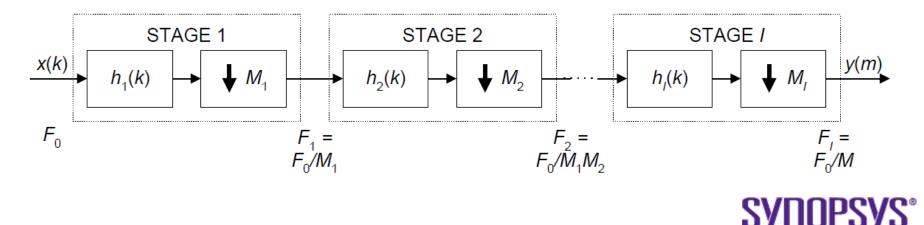

## **MULTISTAGE DECIMATORS**

- A decimation filter can be realized by cascading several stages

- The decimation ratio must be factored into the product of integer numbers

$$M = \prod_{i=1}^{l} M_i$$

## **TYPES OF DECIMATION FILTERS**

### Halfband-

Flat frequency response

Difficult enough management

**CIC-filters**

lters

Multiply-free filters

Narrow pass-band in relation to the sample rate

and large external control

Not need a complex synchronization

The width of registers increases with increase in factor frequency change. Contain in its structure multipliers

Bad suppression in the stop-band

The general filter used in PDC designs is a halfband product. The halfband is also typically implemented as a fixed coefficient filter, however it also represents a less efficient implementation than the CIC. Its frequency response is characterized by a very flat pass-band.

## FILTERS FREQUECY RESPONSES

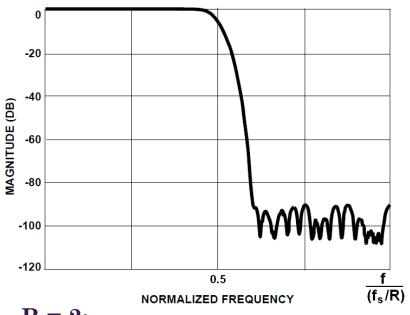

#### Halfband

#### **R** = 2:

The **pass-band** usually has less than 0.0003 dB of ripple from 0fs to 0.2fs **Stop-band** attenuation of greater than 90dB from 0.3fs to Nyquist.

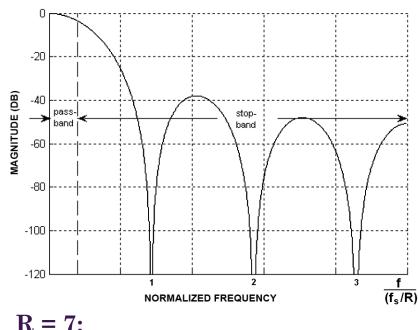

CIC

**R** = 7: Frequency bands in the interval:

k/M fc, k = 1, 2,... [ R/2 ], fc ~ 1/8fs

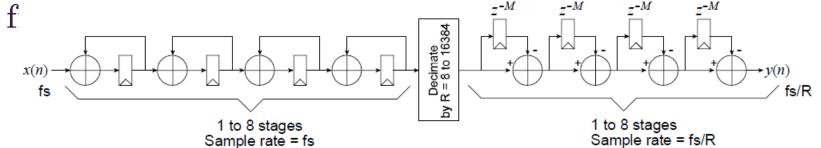

## **CIC-FILTERS**

CIC-Cascaded integrator-comb

Basic characteristics of CIC-filters:

- N number of CIC-stages

- R decimation rate change

- $\mathbf{M}$  differential delay in the comb section stages of the

The implementation of this filter response with a clever combination of comb filter sections, integrator sections, and downsampling for decimation give rise to the hardware-efficient implementation of CIC-filters.

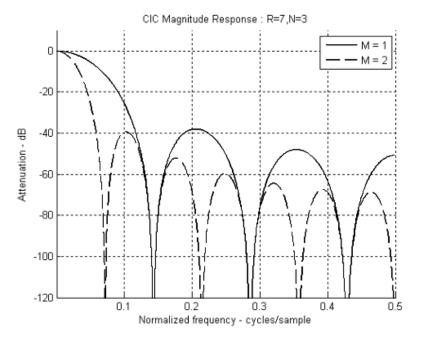

## **CIC MAGNITUDE RESPONSE**

#### Effect of differential delay M:

**Normalized frequency** is the discretetime frequency, normalized to the higher frequency in a rate changing filter - input sampling frequency in a CIC decimation.

This shows the effect of the differential delay **M** on the magnitude response of a filter with 3 stages (N = 3) and a sample rate change R = 7. Besides the effect on the placement of the response nulls, increasing **M** also increases the amount of attenuation in side lobes of the magnitude response.

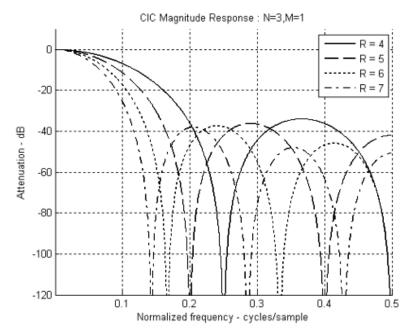

## **CIC MAGNITUDE RESPONSE**

#### Effect of rate change R:

**Normalized frequency** is the discretetime frequency, normalized to the higher frequency in a rate changing filter - input sampling frequency in a CIC decimation.

The effect of **R** on the magnitude response can be seen in this figure. In essence, increasing the rate change increases the length of the cascaded unit-amplitude, rectangular window of length  $\mathbf{R}^*\mathbf{M}$ . This results in an increase in attenuation and decrease of the width of the response side lobes.

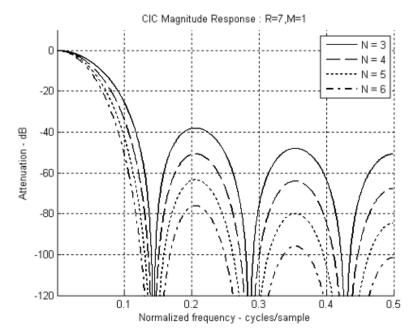

## **CIC MAGNITUDE RESPONSE**

#### Effect of number of stages N:

**Normalized frequency** is the discretetime frequency, normalized to the higher frequency in a rate changing filter - input sampling frequency in a CIC decimation.

Increasing **N** has the effect of increasing the order of the zeros in the frequency response. This, in turn, increases the attenuation at frequencies in the locality of the zero. This effect is clearly illustrated in this figure where we see increasing attenuation of the filter sidelobes as **N** is increased.

## **CIC CORE**

#### Standard I/O interface of CIC core

| – DIN[B-1:0]<br>– ND | DOUT[W-1:0] | NAME        | DIRECTIO<br>N | DESCRIPTION                   |  |  |  |  |  |  |

|----------------------|-------------|-------------|---------------|-------------------------------|--|--|--|--|--|--|

|                      |             | CLK         | Input         | Clock                         |  |  |  |  |  |  |

| ─ LD_DIN* ─ WE*      | * RDY       | DIN         | Input         | Data Input                    |  |  |  |  |  |  |

| - CLK                |             | ND          | Input         | New Data                      |  |  |  |  |  |  |

| *Optional pin        |             | DOUT        | Output        | Filter Output Sample          |  |  |  |  |  |  |

|                      |             | *RDY        | Output        | Filter Output Sample<br>Ready |  |  |  |  |  |  |

|                      |             | *RDF        | Output        | Ready for Data                |  |  |  |  |  |  |

|                      |             | *LD_DI<br>N | Input         | LD_DIN input bus              |  |  |  |  |  |  |

|                      |             | *WE         | Input         | Write Enable signal           |  |  |  |  |  |  |

|                      |             |             |               | 0/1101 0/0                    |  |  |  |  |  |  |

Predictable Success

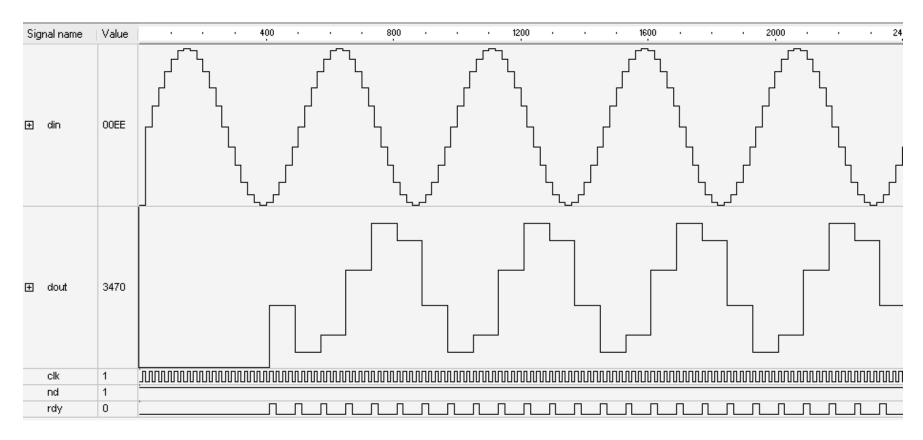

Device and simulation parameters

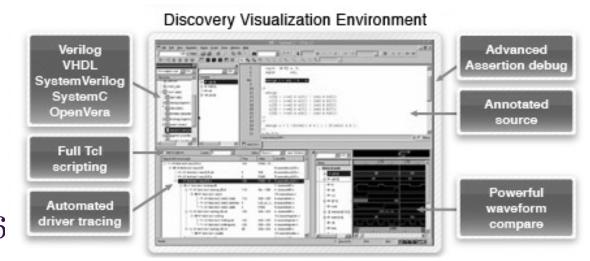

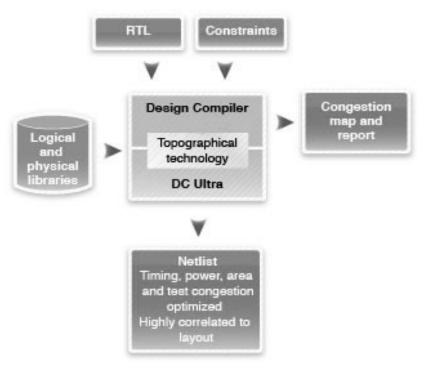

HDL language: Verilog EDA software: Design Compiler, VCS

#### Device parameters:

- **M** = 1

- **N** = 4

- **R** = 4

- width input = 8

- width output = 16

#### Checking main formulas

For CIC decimators, the gain G at the output of the final comb section is:

$$G = (RM)^N$$

If Bin is the number of input bits, then the number of output bits, Bout, is:

$$B_{\text{out}} = [N \log_2 RM + B_{\text{in}}]$$

| Sig | inal name | Value |             | •  | •   | • | 200 | •  | •  | •  | 400 | •    | •            | •  | 600  | •       | •  | •        | 800 | •   | •        | •       | 10  |

|-----|-----------|-------|-------------|----|-----|---|-----|----|----|----|-----|------|--------------|----|------|---------|----|----------|-----|-----|----------|---------|-----|

| +   | din       | 000C  | (0000       |    |     |   |     |    |    |    |     |      |              |    |      |         |    |          |     |     |          |         |     |

| +   | dout      | 0C00  | XXXX        |    |     |   |     |    |    |    | XC  | )COO | <u>xocoo</u> | X  | 0000 | <u></u> | 0  | <u> </u> | `a  | 000 | <u> </u> | _<br>تر | 000 |

|     | clk       | 1     | <u>Г</u> ЛЛ | ЛЛ | ЛЛГ | ய | ՄՄ  | nj | ЛЛ | ЛЛ |     | ЛЛ   | nnn          | UU | UП   |         | ЛЛ | JUU      | UUU | ЛЛ  |          | ЛЛ      | Л   |

|     | nd        | 1     |             |    |     |   |     |    |    |    |     |      |              |    |      |         |    |          |     |     |          |         |     |

|     | rdy       | 0     |             |    |     |   |     |    |    |    |     | 1    |              |    |      |         |    |          |     | 1   |          |         | l   |

$$C'h \bullet (4 \cdot 1)^4 = C00'h$$

(!)

#### Simulation sinusoidal signal

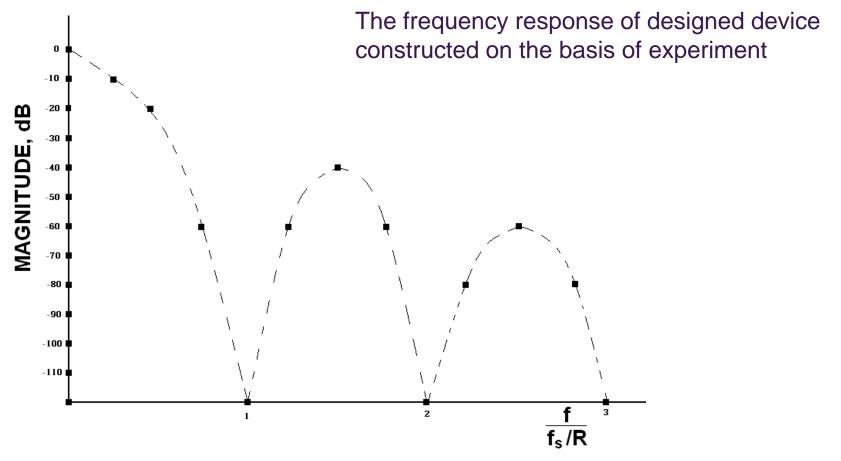

#### Frequency response

## MAIN CHARACTERISTICS

#### All optimization is **off**.

Dynamic power consumption:  ${\sim}830~\mu W$  / clock

Area:  $\sim 12100 \ \mu m^2$

Max frequency:  $\sim 165 \text{ MHz}$

Predictable Success

## APPLICATION

A CIC filter is typically used in applications where the system sample rate is much larger than the bandwidth occupied by the signal.

They are commonly used to build:

- DDCs

- DUCs

Some applications:

- radar systems

- cable modems

- satellite receivers

- 3G base stations

## **THANK YOU**

#### Thanks for your time and attention. Are you questions?