#### Low Power Design Methods: Design Flows and Kits

Shushanik Karapetyan 1st year PhD Student Synopsys Armenia Educational Department, State Engineering University of Armenia

> Moscow March 23, 2011

#### Outline

- Low Power Design Flows

- Library requirements for Low Power Design

- Example of 90nm EDK

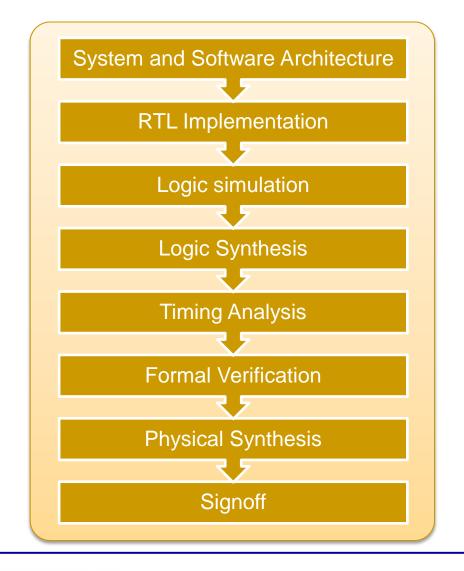

#### **Conventional Design Flow**

**SYNOPSYS**<sup>®</sup>

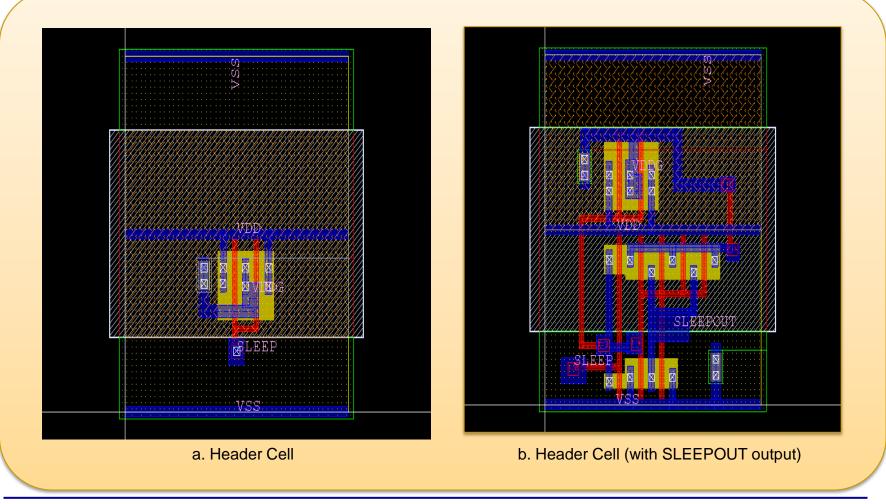

Power Management should be taken into account at the earliest design stages

Almost every step of design flow need to be modified for LPD

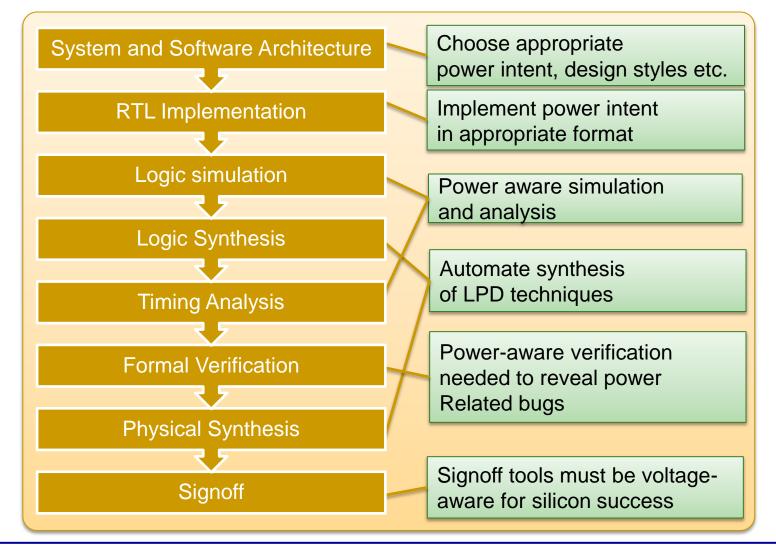

#### **Power-Aware Design Flow**

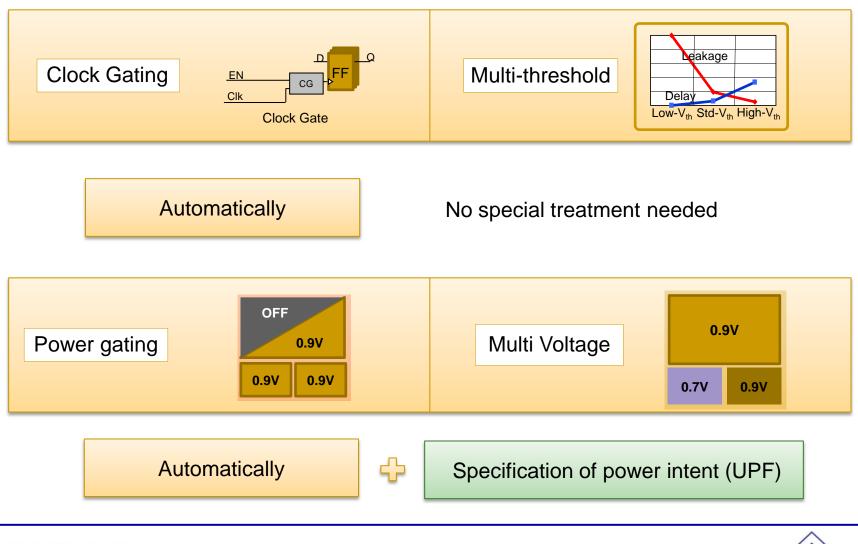

#### **LPD Techniques Automation Levels**

**Synopsys**°

## **Unified Power Format (UPF): Necessity**

| Language                                                      | Specification of power intent | Interoperable<br>among EDA tools | Can be freely used<br>(open standard) |

|---------------------------------------------------------------|-------------------------------|----------------------------------|---------------------------------------|

| Hardware<br>Description<br>Languages<br>(Verilog, VHDL, etc.) | -                             | +                                | +                                     |

| Vendor –Specific<br>Formats                                   | +                             | -                                | -                                     |

| UPF                                                           | +                             | +                                | +                                     |

## **Specifying Power Intent**

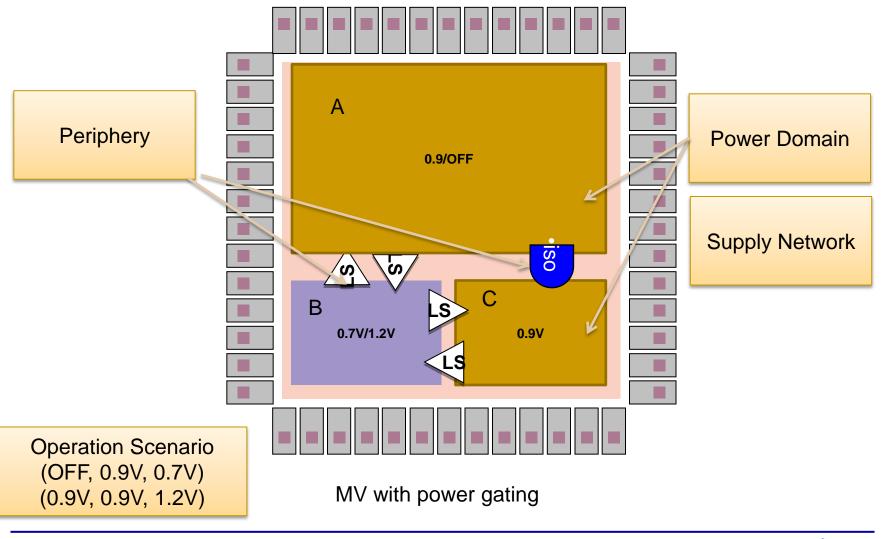

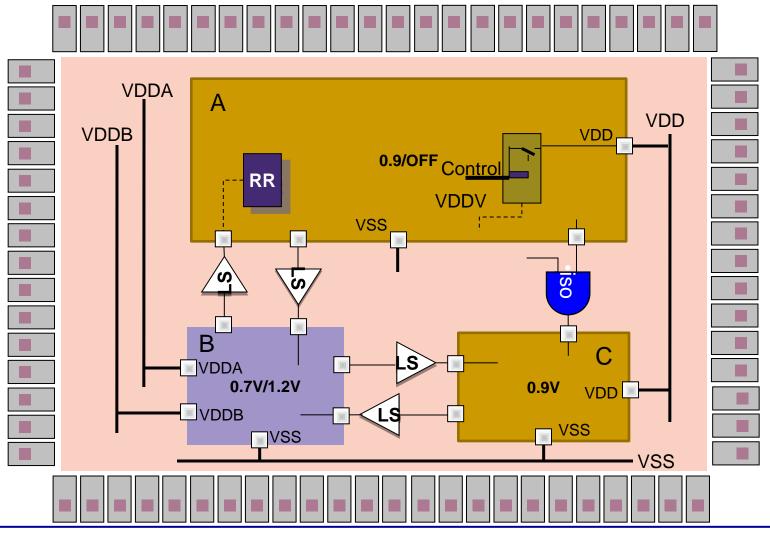

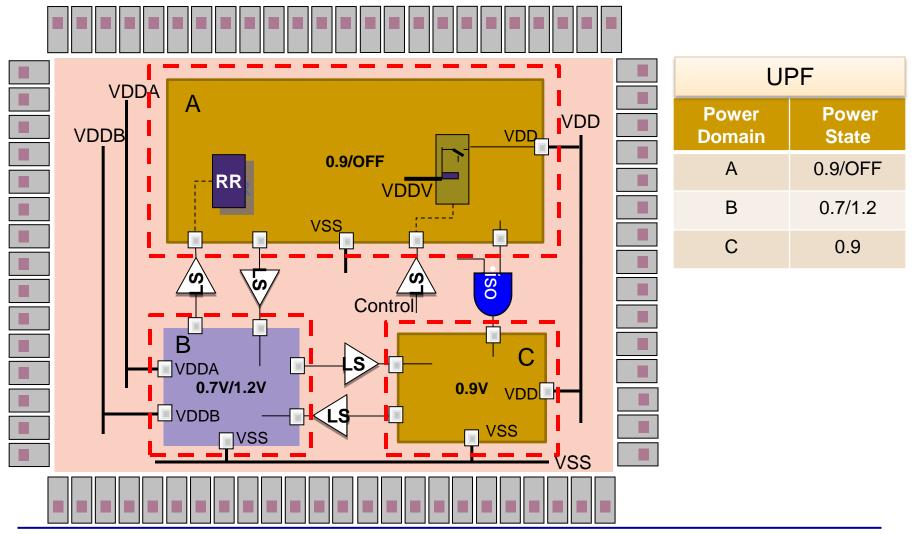

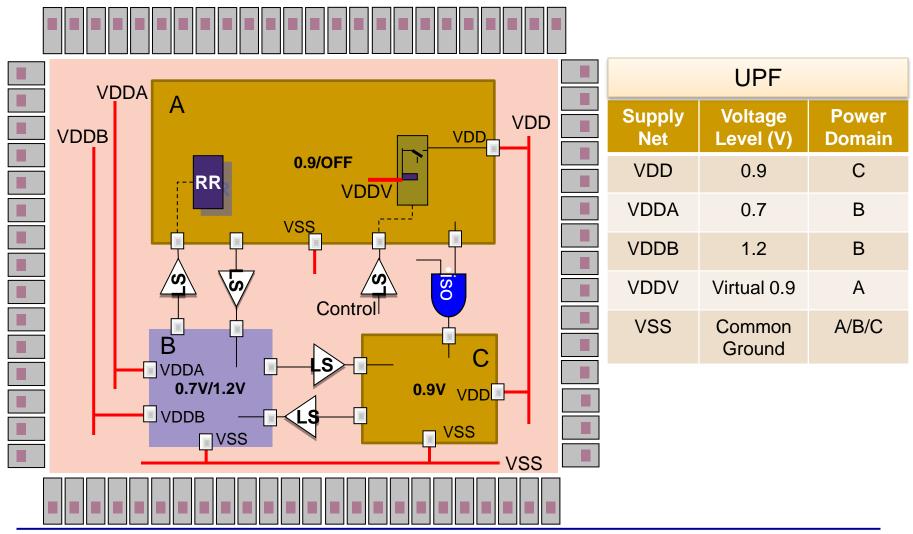

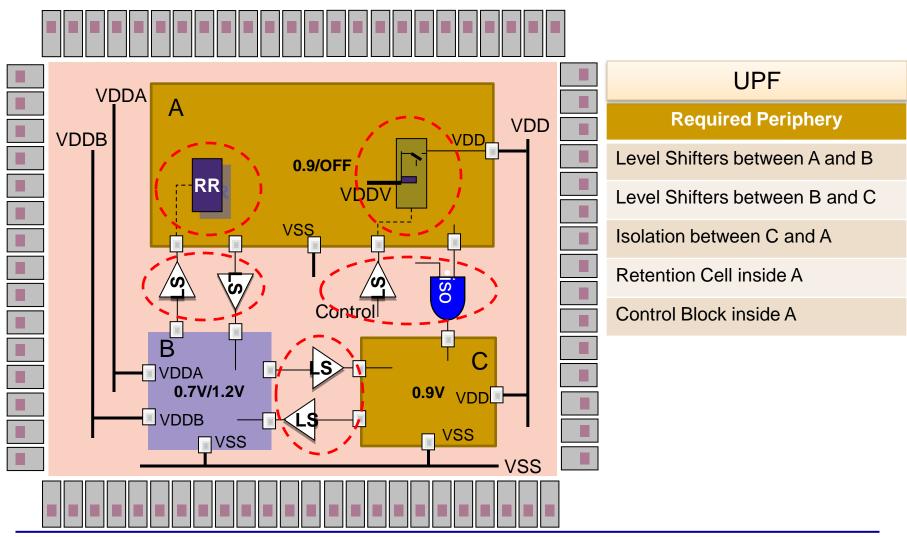

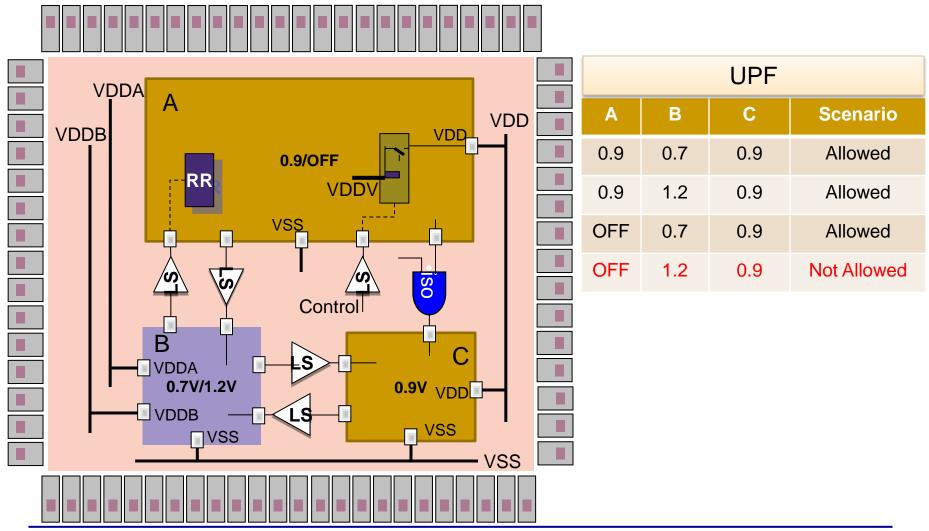

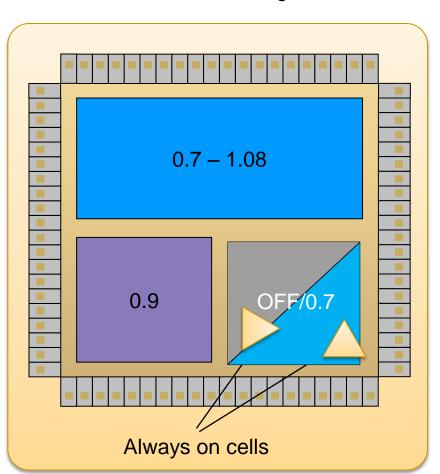

#### **MV with Power Gating Example**

#### **UPF: Power Domains**

#### **UPF: Supply Network**

#### **UPF: Periphery**

#### **UPF: State Scenario**

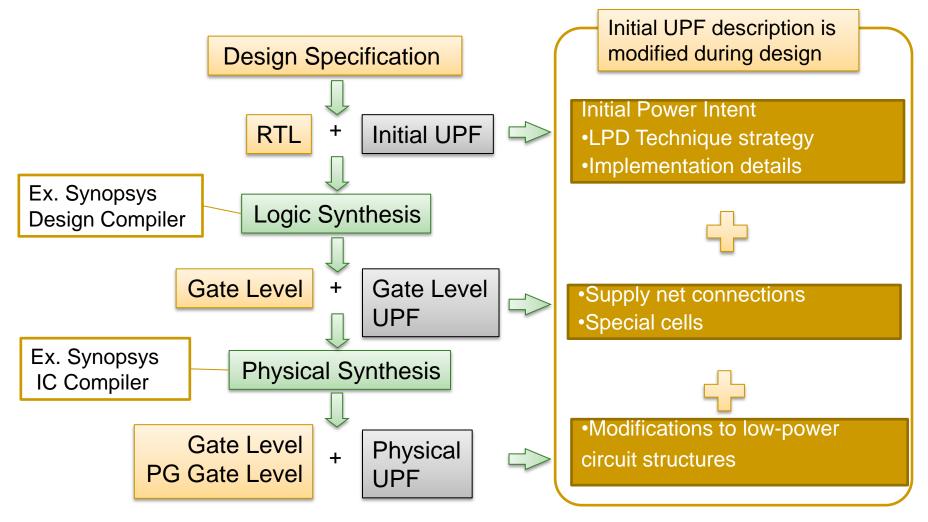

# **Design Flow Modification with UPF**

**SYNOPSYS**<sup>®</sup>

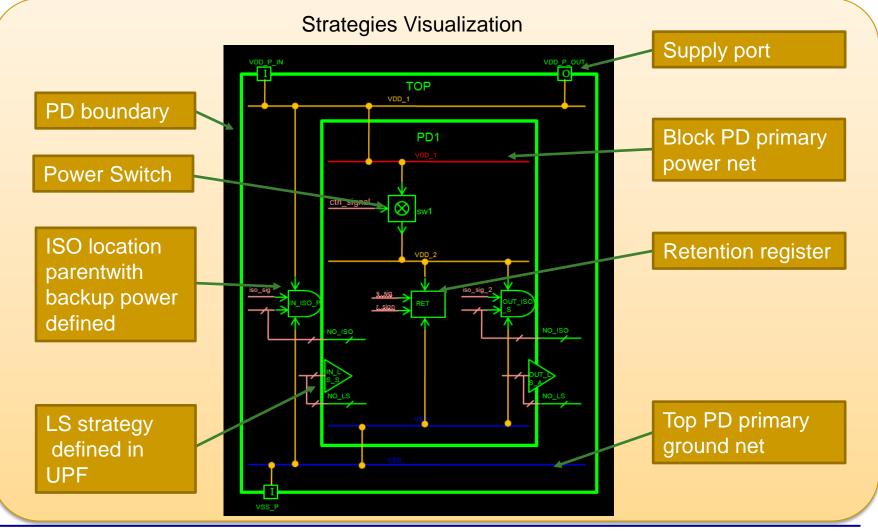

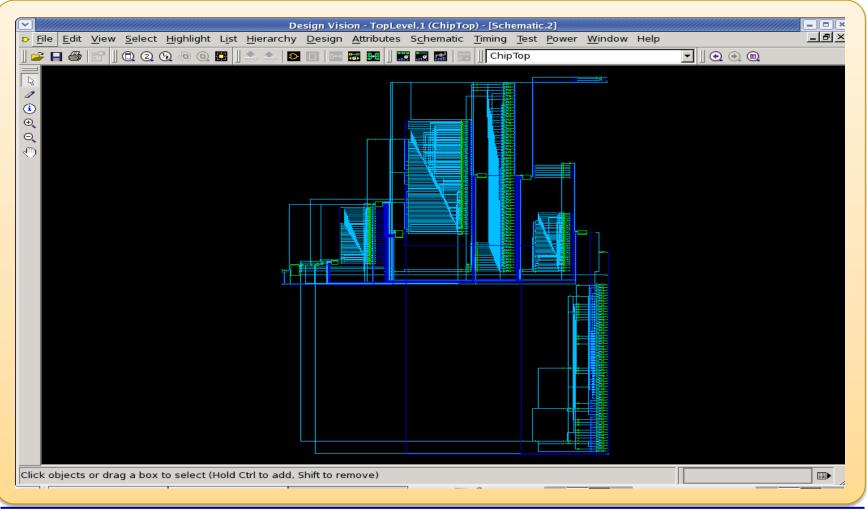

## **Design Compiler Visual UPF**

**SYNOPSYS**°

Copyright © 2011 Synopsys, Inc.

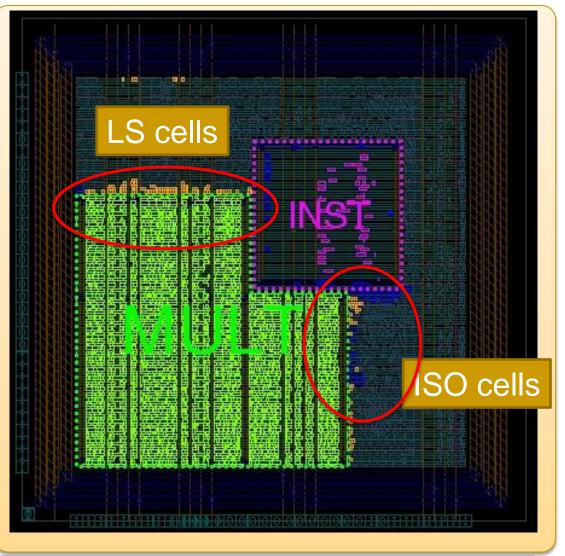

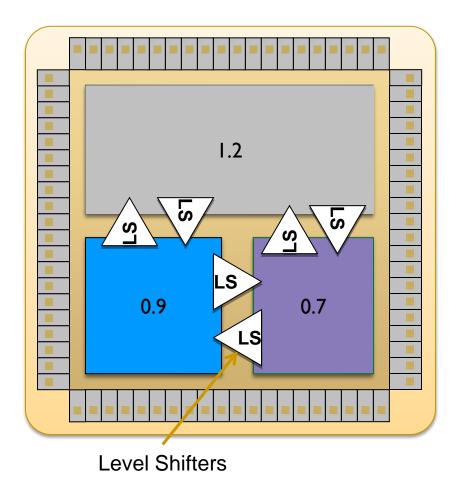

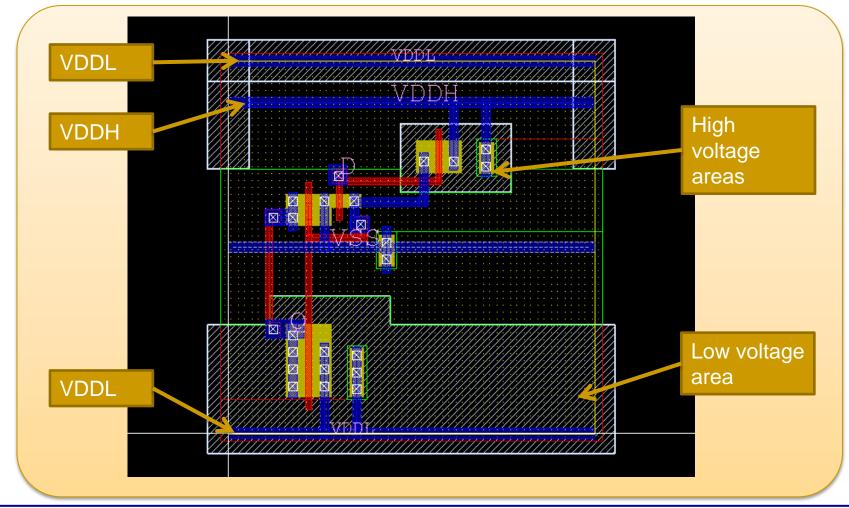

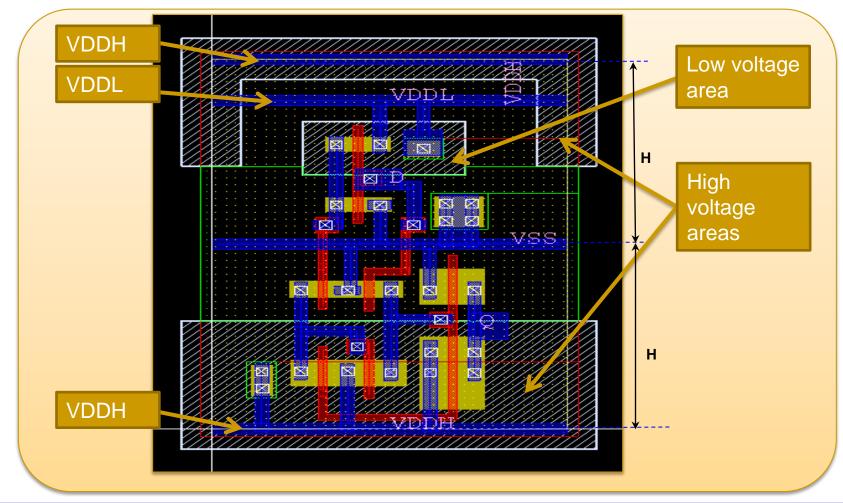

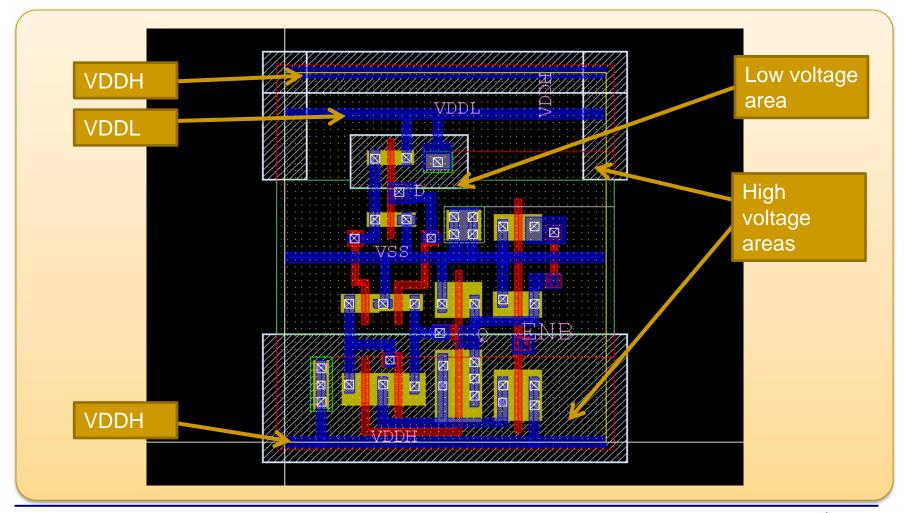

# **IC Compiler UPF Placement**

- Placement respects voltage area boundary

- Special Level Shifter and Isolation Cells placement

- Special cells placed closer to VA boundary

#### Library Requirements for LPD

- Special cells

- Special versions of library

- Characterization in additional corners

- Additional views/files/attributes

## **90nm EDK: Digital Standard Cell Library**

Digital Standard Cell Library (DSCL)

Aimed at optimizing the main characteristics of designed lcs

Contains 340 cells, cell list compiled based on the requirements for educational designs

Typical combinational and sequential logic cells for different drive strengths

Typical combinational and sequential

| Inverters/Buffers | Logic Gates | Flip-Flops<br>(regular+scan) |

|-------------------|-------------|------------------------------|

| Latches           | Delay Lines | Physical<br>(Antenna diode)  |

| Isolation Cells | Level Shifters | Retention<br>Flip-Flops |

|-----------------|----------------|-------------------------|

| Clock gating    | Always-on      | Power Gating            |

Buffers

Special cells for different styles LPD

Provides the support of IC design with different core voltages to minimize dynamic and leakage power.

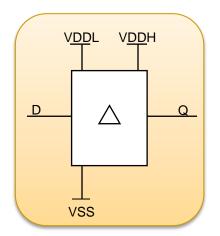

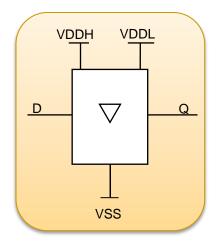

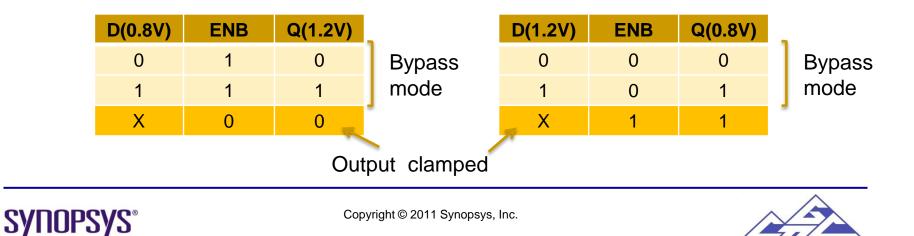

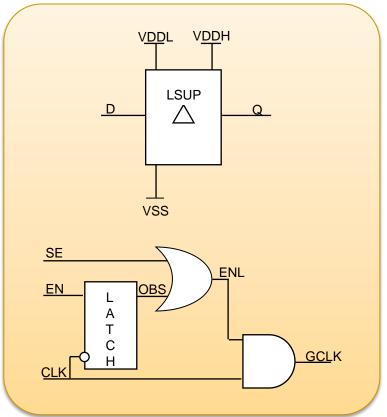

#### **Special Cells for LPD: Level Shifter**

#### **Level Shifter**

Logic Symbol of Low to High Level Shifter

Low to High Level Shifter Truth Table

| D (0.8V) | Q (1.2V) |

|----------|----------|

| 0        | 0        |

| 1        | 1        |

Logic Symbol of High to Low Level Shifter

High to Low Level Shifter Truth Table

| D (1.2V) | Q (0.8V) |

|----------|----------|

| 0        | 0        |

| 1        | 1        |

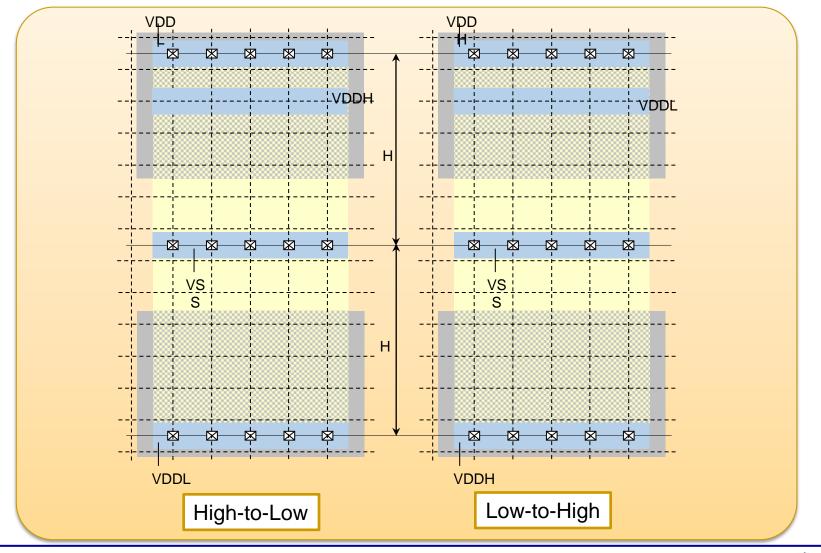

#### **Level Shifter Physical Structure**

#### Level Shifter (High to Low) Physical Design

## Level Shifter (Low to High) Physical Design

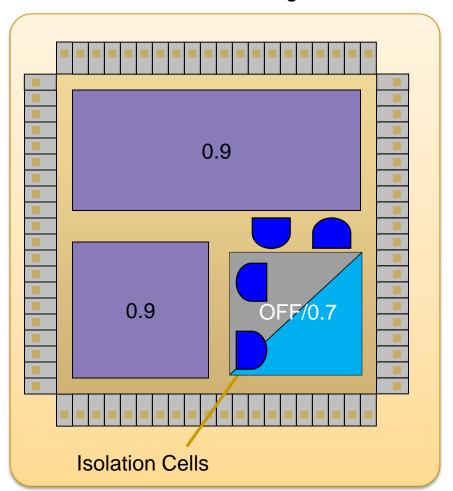

#### **Special Cells for LPD: Isolation Cells**

Power Gating

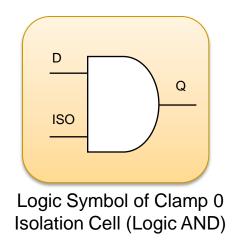

#### **Isolation Cells**

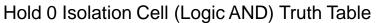

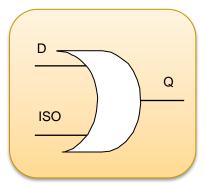

Logic Symbol of Clamp 1 Isolation Cell (Logic OR)

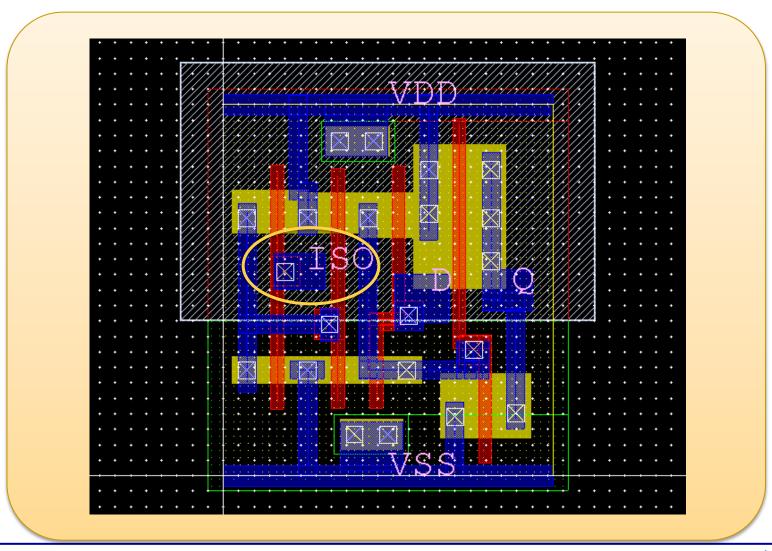

#### **Isolation Cells: Physical Design**

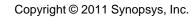

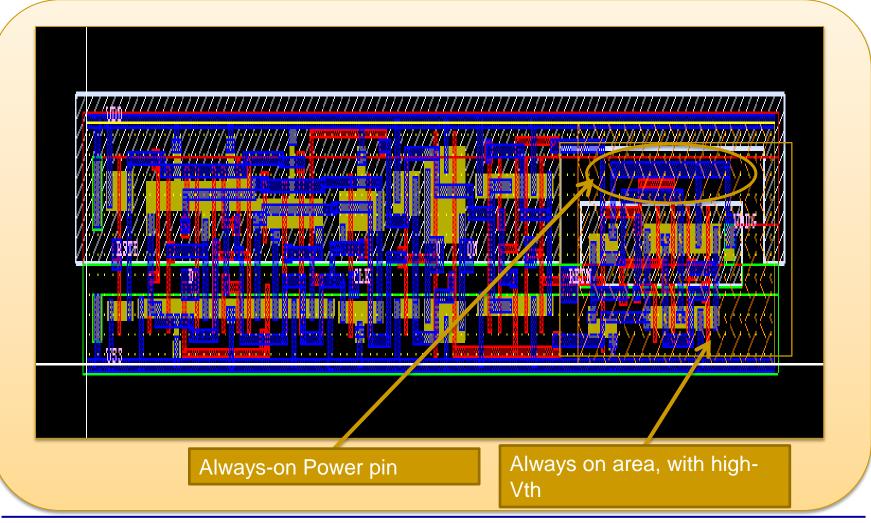

#### **Special Cells for LPD: Always-on Buffers**

Power Gating

#### **Always-on Buffer**

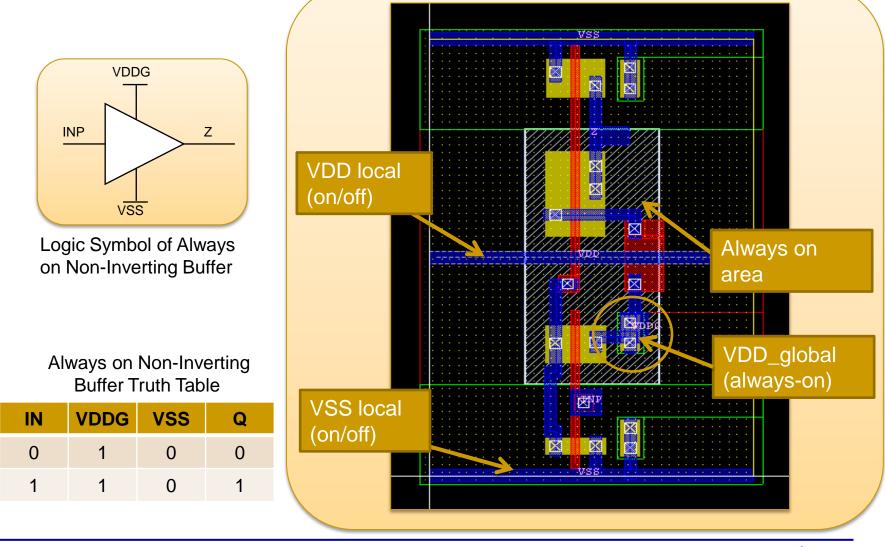

#### **Special Cells for LPD: Always-on Isolation cells**

#### **Always on Isolation Cells**

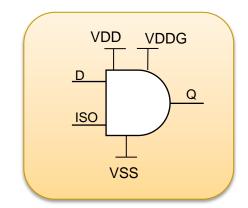

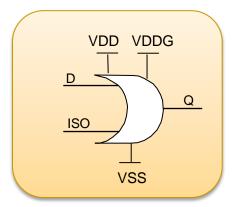

Logic Symbol of Clamp 0 Isolation Cell (Logic AND), Always On

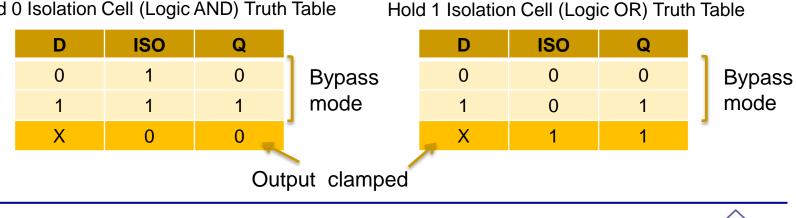

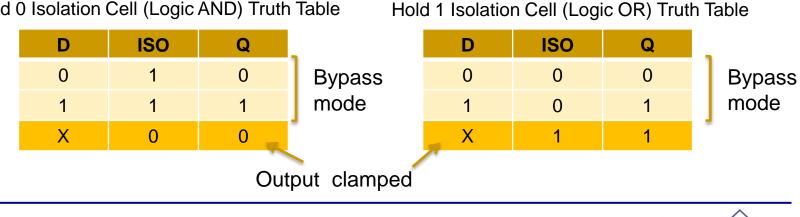

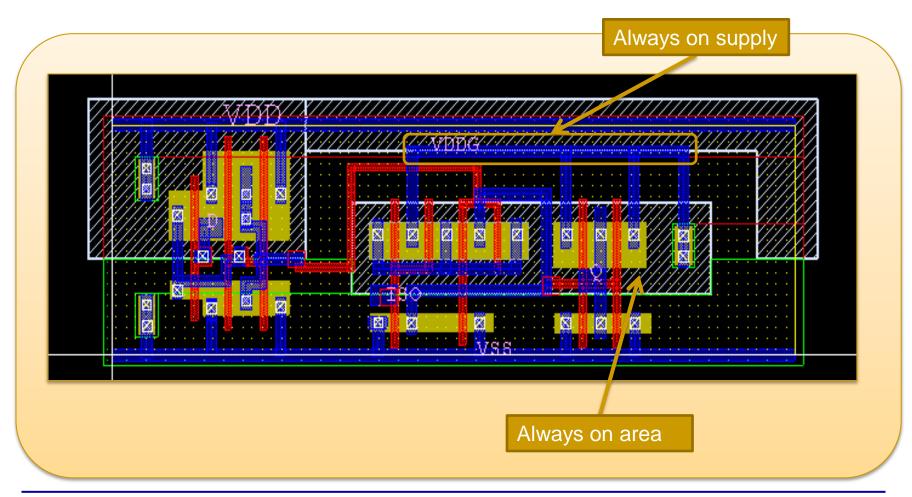

Hold 0 Isolation Cell (Logic AND) Truth Table

Logic Symbol of Clamp 1 Isolation Cell (Logic OR), Always On

**SYNOPSYS**<sup>®</sup>

Copyright © 2011 Synopsys, Inc.

## Isolation Cell (always-on) Physical Design

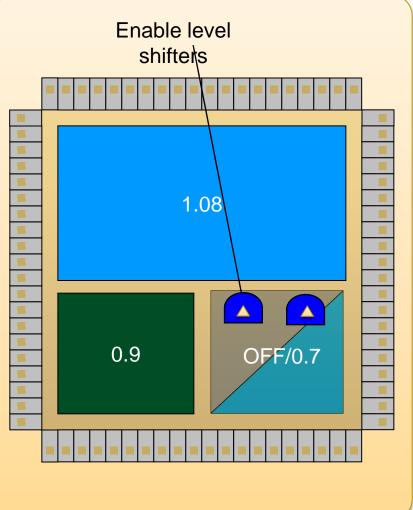

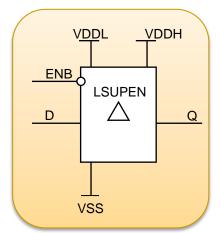

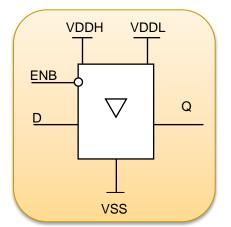

# Special Cells for LPD: Enable level shifters

Combination of Level Shifter and ISO cell

#### **Level Shifters With Active Low Enable**

Symbol of Low to High Level Shifter Active Low Enable, Clamp 0

Symbol of High to Low Level Shifter Active Low Enable, Clamp 1

#### Enable Level Shifter (low-to-high) Physical design

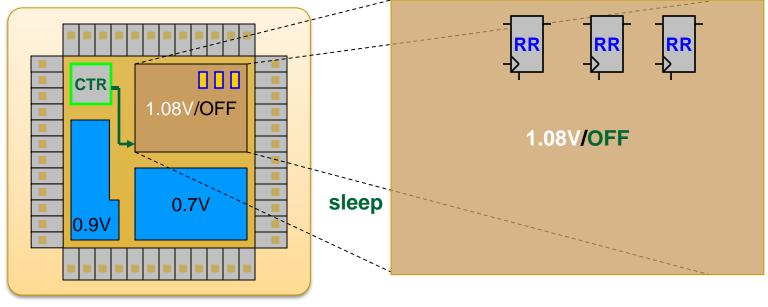

#### **State Retention Registers**

#### **State Retention Registers**

• Retention Register - preserve status while the logic is turned off

#### **Retention Register Physical design**

**SYNOPSYS**°

Copyright © 2011 Synopsys, Inc.

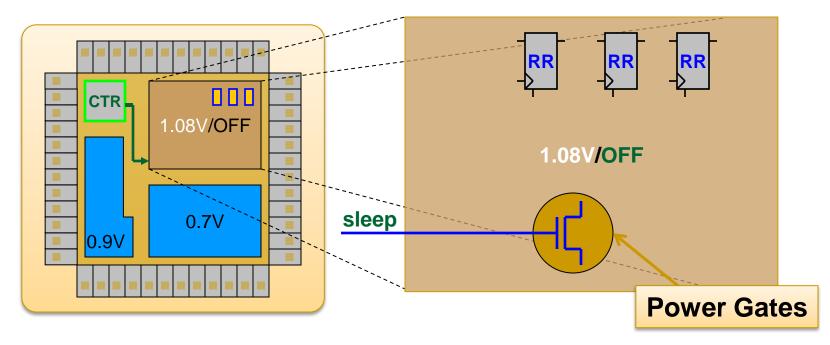

#### **Power Gates**

- Retention Register preserve status while the logic is turned off

- Coarse Grain Power Gates

(switch cells)

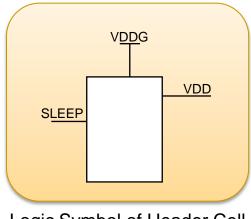

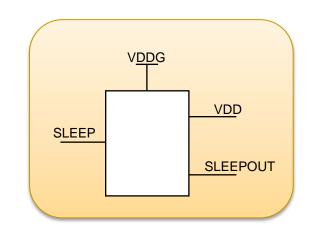

#### **Header Cells**

Logic Symbol of Header Cell

Logic Symbol of Header Cell(with SLEEPOUT output )

#### Header Cell Truth Table

| SLEEP | VDDG | VDD  |

|-------|------|------|

| 0     | 1    | 1    |

| 1     | 1    | hi-z |

**SYNOPSYS**<sup>®</sup>

Header Cell (with SLEEPOUT output) Truth Table

| SLEEP | VDDG | VDD  | SLEEPOUT |

|-------|------|------|----------|

| 0     | 1    | 1    | 0        |

| 1     | 1    | hi-z | 1        |

#### **Header Cells Physical Design**

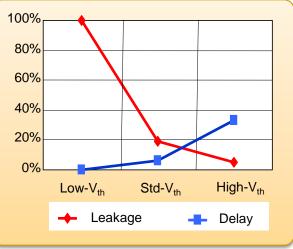

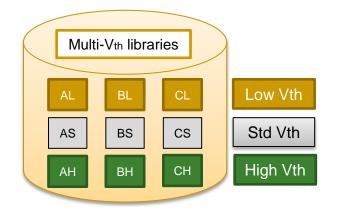

#### **Multi-Threshold Libraries**

#### **DSCL: Multi Threshold Versions of Cells**

- For implementation of Multi-Vth technique the whole DSCL is available in 3 versions (1020 cells)

- All cells with Low– threshold voltage

- All cells with Standard threshold voltage

- All cells with High— threshold voltage

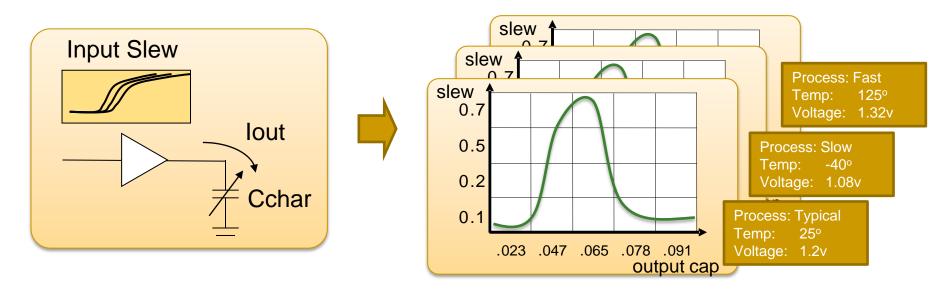

#### Characterization

**SYNOPSYS**<sup>®</sup>

- Characterization computes cell parameter (e.g. delay, output current) depending on input variables: output load, input slew, etc.

- Characterization is preformed for various combinations of operating conditions: process, voltage, temperature (also called PVT corners).

#### **DSCL: Characterization Corners**

| Corner<br>Name                   | Process<br>(NMOS proc. –<br>PMOS proc.) | Temperature (T) | Power Supply (V) | Notes                  |

|----------------------------------|-----------------------------------------|-----------------|------------------|------------------------|

| TTNT1p20v                        | Typical - Typical                       | 25              | 1.2              | Typical corner         |

| SSHT1p08v                        | Slow - Slow                             | 125             | 1.08             | Slow corner            |

| FFLT1p32v                        | Fast - Fast                             | -40             | 1.32             | Fast corner            |

| FFHT1p32v                        | Fast - Fast                             | 125             | 1.32             | High leakage corner    |

| SSLT1p32v                        | Slow - Slow                             | -40             | 1.32             | Low temperature        |

| SSLT1p08v                        | Slow - Slow                             | -40             | 1.08             | corners                |

| Low Voltage Operating Conditions |                                         |                 |                  |                        |

| TTNT0p80v                        | Typical - Typical                       | 25              | 0.80             | Typical corner         |

| SSHT0p70v                        | Slow - Slow                             | 125             | 0.70             | Slow corner            |

| FFLT0p90v                        | Fast - Fast                             | -40             | 0.90             | Fast corner            |

| FFHT0p90v                        | Fast - Fast                             | 125             | 0.90             | High leakage<br>corner |

| SSLT0p90v                        | Slow - Slow                             | -40             | 0.90             | Low temperature        |

| SSLT0p70v                        | Slow - Slow                             | -40             | 0.70             | corners                |

#### **SYNOPSYS**°

### **DSCL: Additional Data**

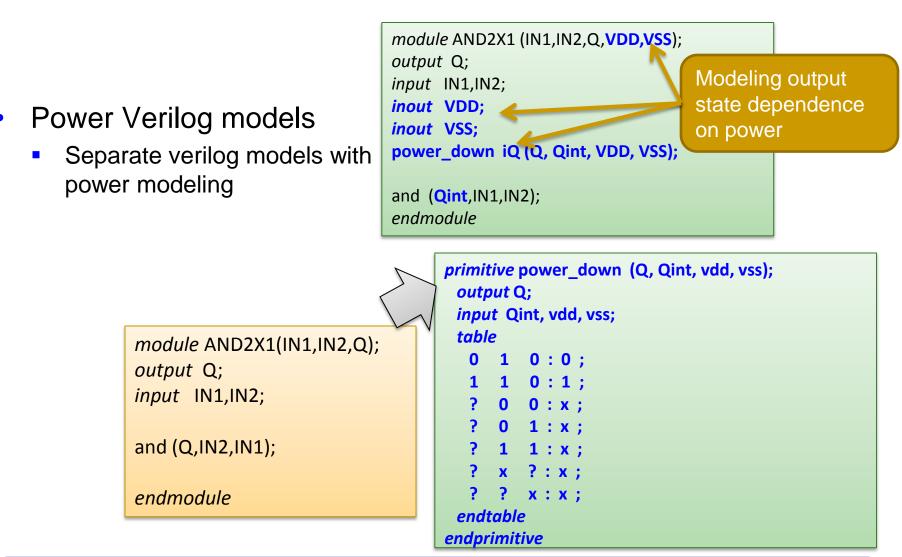

- Power / ground (PG) pin definitions are required for all cells in a library

- Defined as attributes in .lib

- Allows accurate definition of multiple power / ground pin information

- Benefits

- Power domain driven synthesis

- Automatic power net connections

- PST-based optimization

- Verification of PG netlist vs. power domains

- Power switch verification

```

pg_pin(VDD) {

std_cell_main_rail : true ;

voltage_name : VDD;

pg_type : primary_power;

}

pg_pin(VSS) {

voltage_name : VSS;

pg_type : primary_ground;

}

```

#### **DSCL: Power Verilog Models**

### DSCL: Special Cells for Low Power Techniques (1)

- Power Gatings

- 5 cells with different loads

- Always on

- 10 cells: 3 inverters, 3 buffers and 4 DFFs

- Retention cells

- 44 cells negedge/posedge, scan

- Isolation cells

- 8 cells with different logic, load

### DSCL: Special Cells for Low Power Techniques (2)

- Level shifters

- 16 cells Low/High, High/Low, with or without enable, with different loads

- Clock gatings:

- 11 cells with different loads, edges, and control (post/pre)

- HVT Cells

- All logical cells are designed using HVT, LVT

#### DSCL: Special Cells for Low Power Techniques (3)

|                            |                                                                        | Power Gates<br>(MTCMOS) | Isolation<br>Cells | Level Shifters | Retention<br>Registers | Always On<br>Logic |

|----------------------------|------------------------------------------------------------------------|-------------------------|--------------------|----------------|------------------------|--------------------|

| 0.9V<br>0.9V 0.9V          | Multiple Power<br>Domains<br>Single Voltage                            |                         |                    |                |                        |                    |

| 0.9V<br>0.7V 0.9V          | Multiple Voltage<br>(MV)<br>Domains                                    |                         |                    | +              |                        |                    |

| OFF<br>0.9V<br>0.9V        | Power Gating<br>(shut down)<br>Single Voltage<br>No State<br>Retention | +                       | +                  |                |                        | +                  |

| OFF<br>0.9V<br>0.7V 0.9V   | MV Domains<br>Power Gating<br>No State<br>Retention                    | +                       | +                  | +              |                        | +                  |

| OFF<br>S 0.9V<br>0.7V 0.9V | MV Domains<br>Power Gating<br>State Retention                          | +                       | +                  | +              | +                      | +                  |

**SYNOPSYS**°

# Low Power Design of ChipTop Developed with DSCL: DC view

## Low Power Design of ChipTop Developed with DSCL: ICC View

| IC Compiler - LayoutWindow.1 - Block Implementation - ChipTop_finish.CEL;1 [write] L      |                             |

|-------------------------------------------------------------------------------------------|-----------------------------|

| File Edit View Select Highlight Floorplan Preroute Placement Clock Route Signoff Finishir |                             |

| ▋┢ 🗛 🗴 🔍 🔍 🔍 🖤 📉 📗 🕶 🗶 🗶 💥 📕 🛄 📿 Q 🕲 🐵 🔍 🔛 🗍 💽 🗨 🖳                                        |                             |

| Input mode C Rectangle Intersect Selection                                                |                             |

| Smart C Line F Enable                                                                     |                             |

|                                                                                           | Voltage Areas               |

|                                                                                           |                             |

|                                                                                           | Apply Reload Options:       |

|                                                                                           | Level Shifters (Regular) 10 |

|                                                                                           | Level Shifters (Enable) 128 |

|                                                                                           | Always-On Cells 43          |

|                                                                                           | Isolation Cells             |

| 🛱 Brightness: 33% 🔽 View Level: 0 🚊 📲 📲 🖬 🖓                                               | I Tie-Off Cells 0           |

| X Objects Layers Settings                                                                 | MTCMOS Cells 3527           |

|                                                                                           | GPRS 1                      |

|                                                                                           | Cells of GPRS 5679          |

|                                                                                           |                             |

| B'B Core Area  Image: Core Area    Ett Port  Image: Core Area                             | Cells of MEMY 232           |

| Terminal                                                                                  |                             |

|                                                                                           | Cells of MULT               |

|                                                                                           | Cells of GENPP              |

| Site Row                                                                                  |                             |

| Bound III III IIII IIIIIIIIIIIIIIIIIIIIIII                                                | Cells of MEMX 232           |

| O Plan Group 🔽 🗹 📰                                                                        |                             |

| 🕘 🕑 Placement Blockage 🔽 🔽                                                                |                             |

|                                                                                           |                             |

| RP Keepout                                                                                |                             |

| · Voltage Area □ □ □                                                                      |                             |

|                                                                                           |                             |

| Click objects or drag a box to select (Hold Ctrl to add, Shift to remove)                 | 2015.628, 2743.026          |

|                                                                                           |                             |

**SYNOPSYS**<sup>®</sup>

#### Conclusion

- Low Power Design requires significant design flow modifications

- UPF enables LPD flow automation

- Low Power design techniques have their huge impact on libraries

- SAED 90nm EDK DSCL includes all special cells needed for low power design techniques

- This 90nm EDK is currently in use in 235 universities of 37 countries

- This 90nm EDK is used inside Synopsys for education of customers

- Currently similar EDK is being developed for 32/28nm technology, initial release is planned in June 2011