Analysis of schematic approaches for reducing the static power consumption of VLSI and SoC functional blocks.

> Volobuev P. 2-d year graduate student in the Master's program Moscow Institute of Electronic Technology

### Background

### Transistor size becomes smaller and smaller

Transistors become faster and faster

High density

## Increase of leakage power

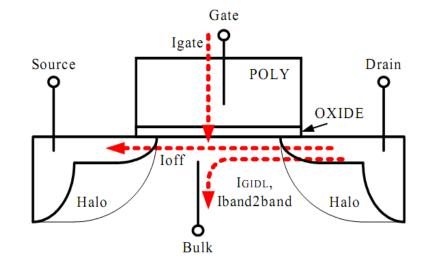

#### Leakage power sources

Subthreshold leakage  $\checkmark$  Leakage increases exponentially as V<sub>T</sub> decreases ✓ Short-channel effect: channel controlled by drain

$$I_{sub} = \frac{\mu WC_{ox}}{L} V_T^2 e^{\frac{|V_{GS}| - |V_t|}{\eta V_T}} \left( 1 - e^{\frac{-|V_{DS}|}{V_T}} \right)$$

• Gate-oxide leakage  $\checkmark$  Gate tunneling due to thin oxide

# Schematic approaches for reducing the static power: classification

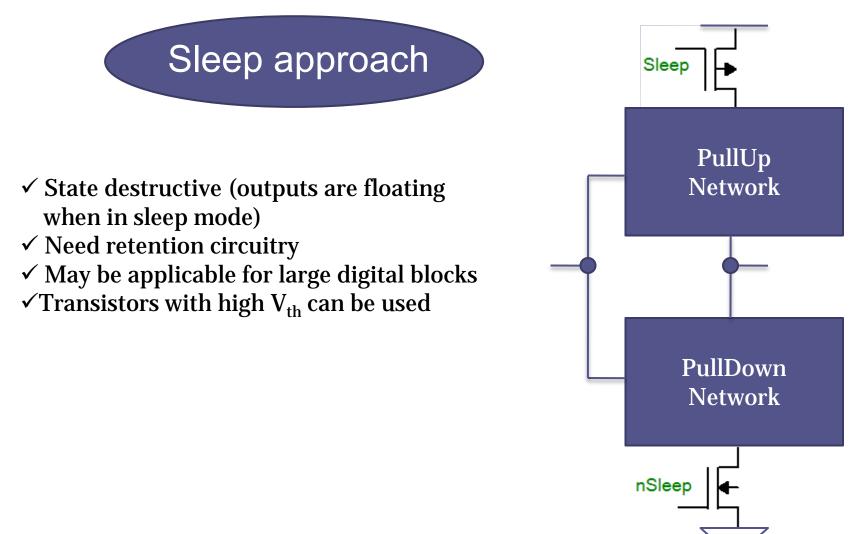

Statedestructive techniques

✓ Sleep approach✓ Zig-zag approach

Statepreserving techniques

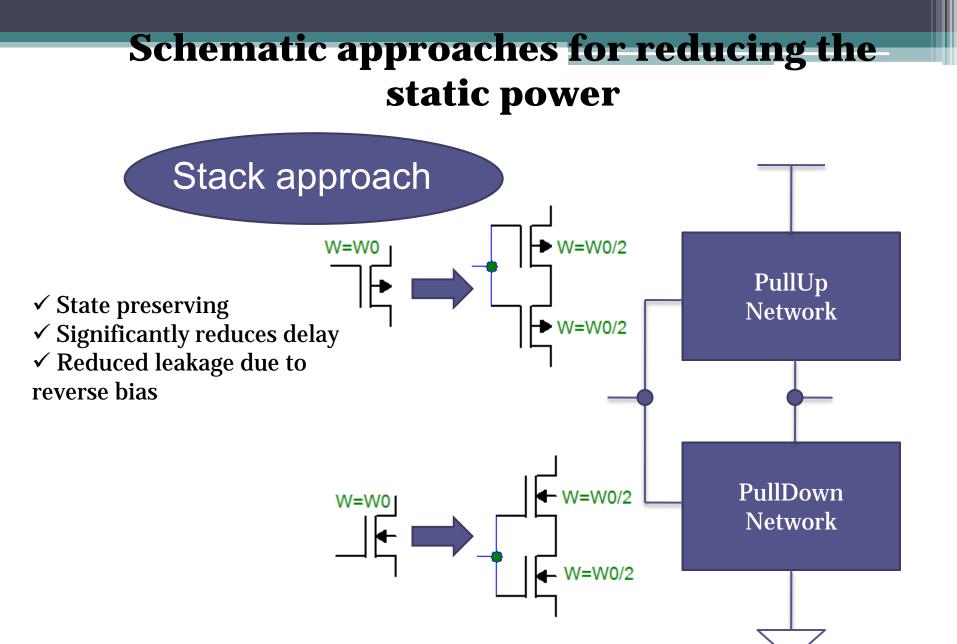

- ✓ Stack approach

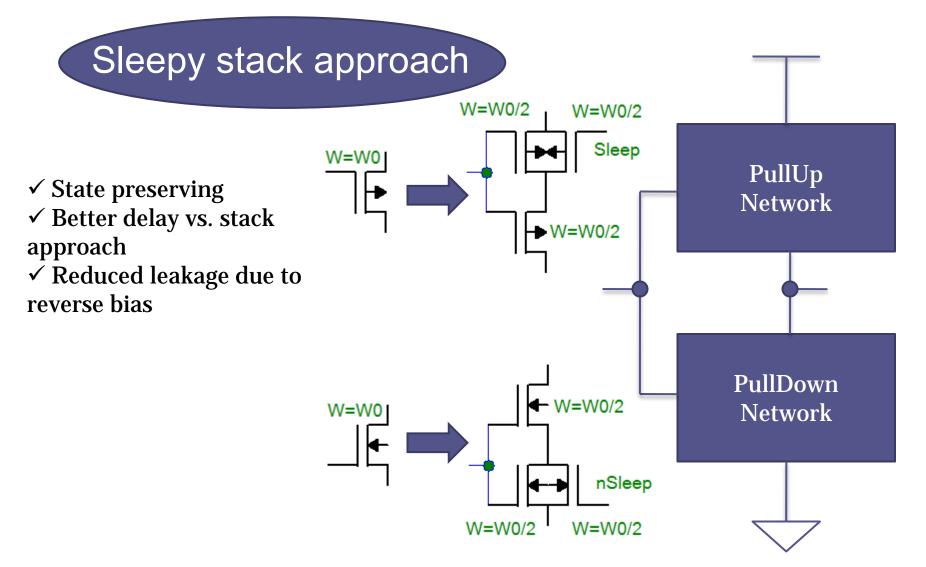

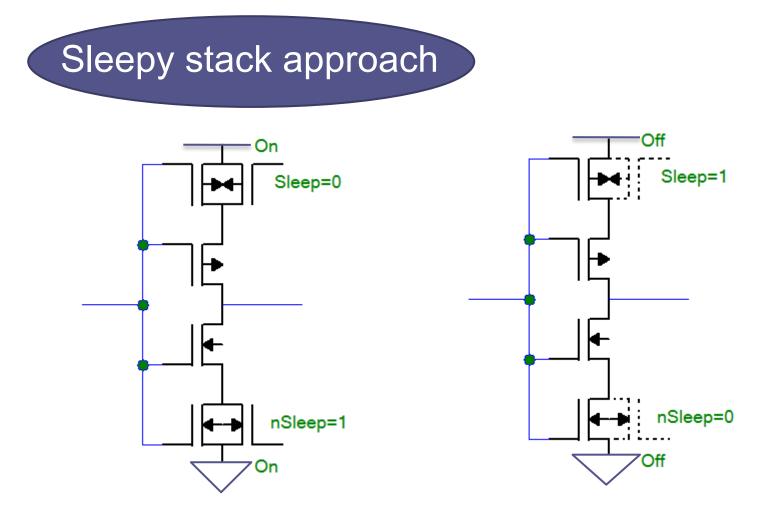

- ✓ Sleepy stack approach

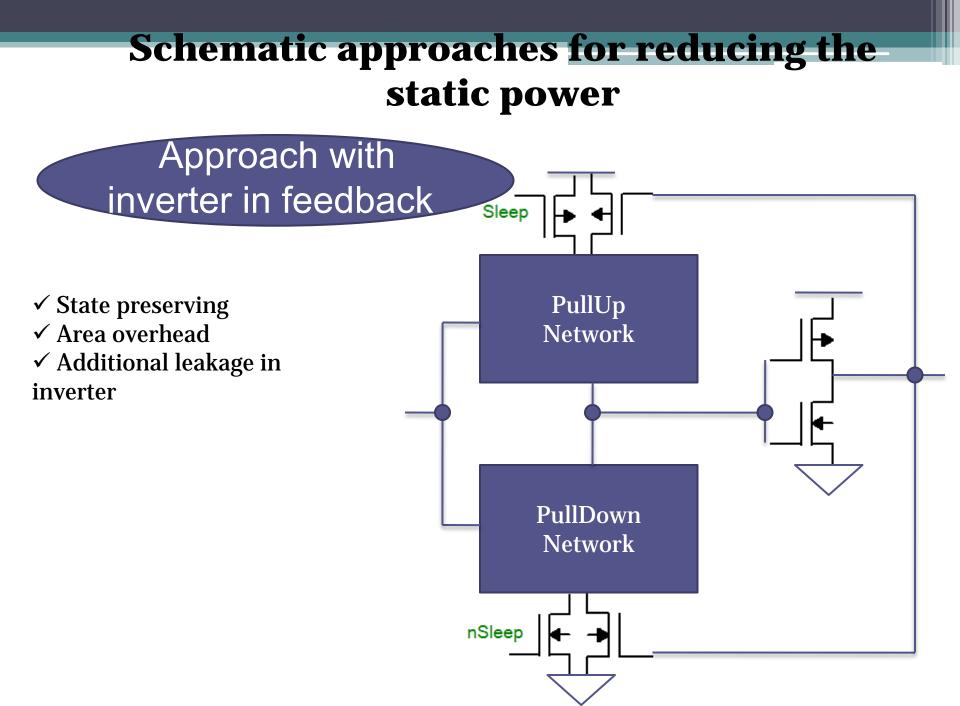

- ✓ Feedback using inverter

- ✓ Sleepy keeper

Active mode – decreases the resistance path

Sleep mode – like stack approach

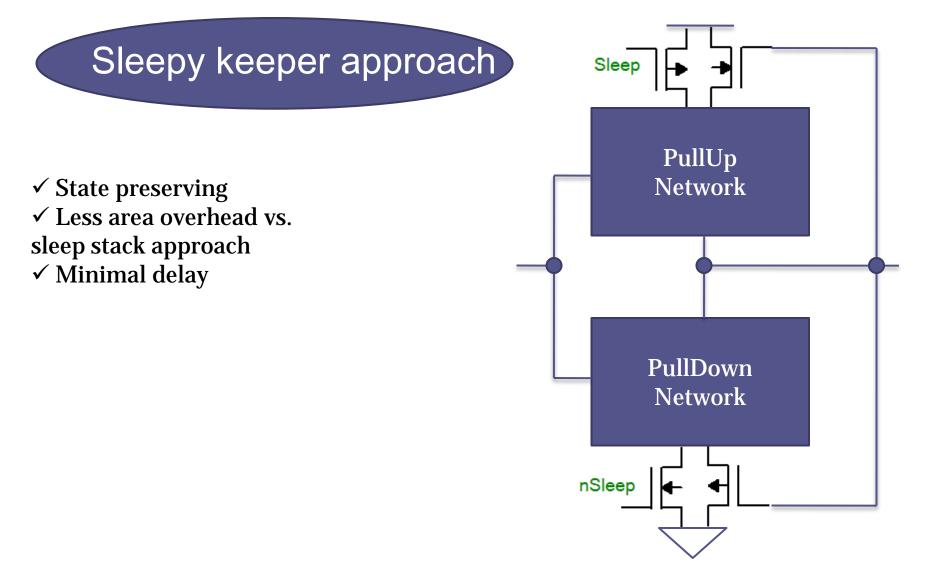

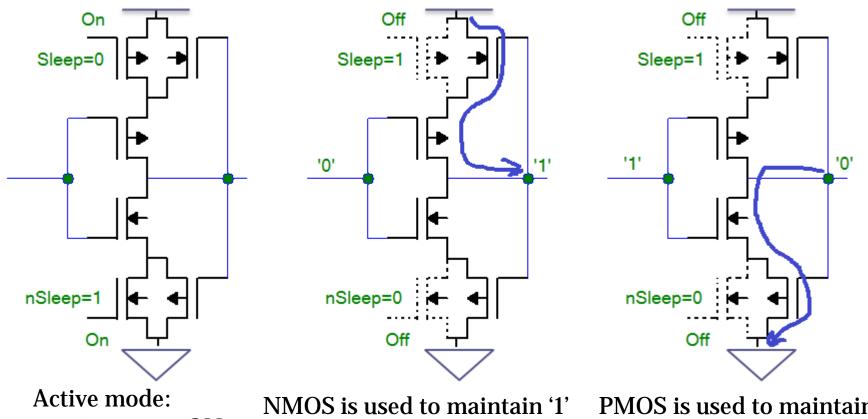

# Sleepy keeper approach

sleep transistors are ON reducing delay MOS is used to maintain '1 in sleep mode PMOS is used to maintain '0' in sleep mode

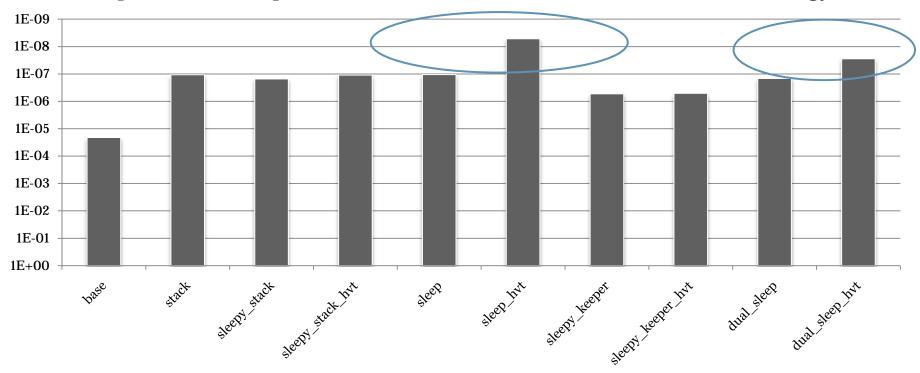

Static power consumption of 4-bit adder realization for 90 nm technology, W

✓ Stack and sleepy\_stack approaches results in roughly 2.5 order of magnitude leakage reduction

✓ Sleepy\_keeper approach results in roughly 1.5 order of magnitude leakage reduction

$\checkmark$  Sleep approach is the leader with 3.5 order

✓ Dual sleep approach (high-Vt) results 3.86X more reduction vs. stack approach and 19X more reduction vs. dual\_sleep

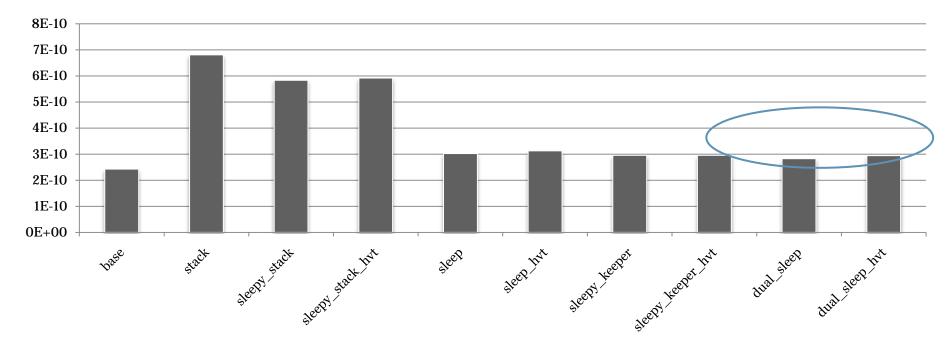

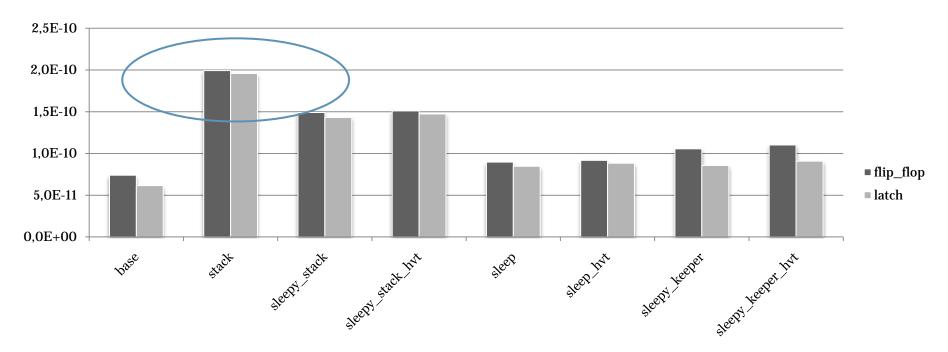

Delay of 4-bit adder realization for 90 nm technology, s

✓ Sleepy\_stack and stack approaches have great delay penalty (up to 2.8X over base case for stack approach)

✓ Sleep and sleepy\_keeper approaches results in best delay over all methods (only 1.2X penalty for sleepy\_keeper approach)

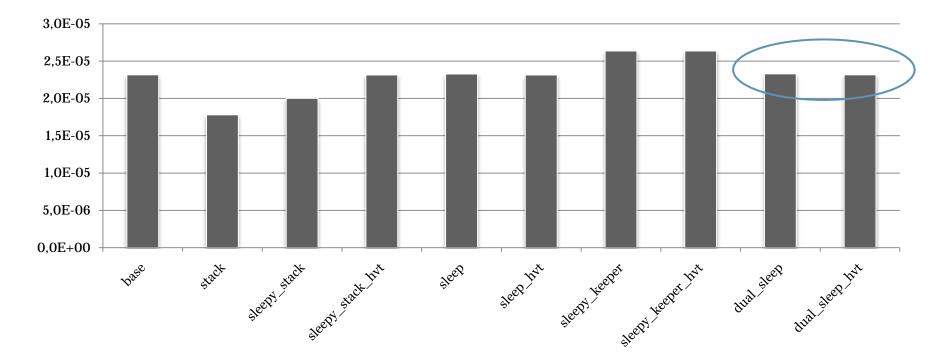

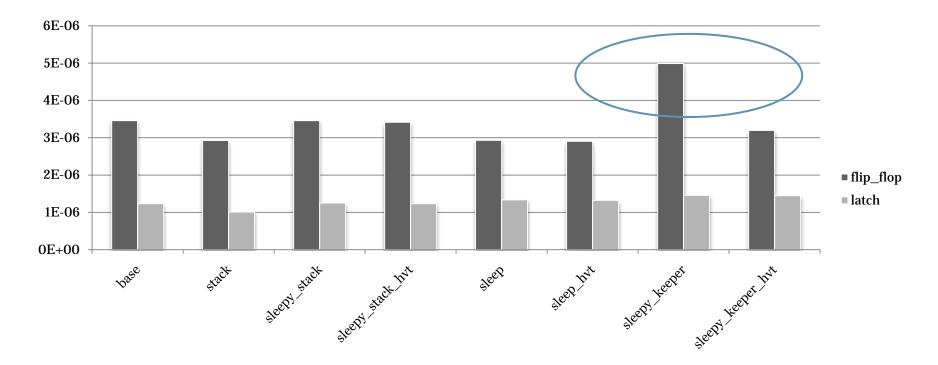

Dynamic power consumption of 4-bit adder realization for 90 nm technology, W

✓ Stack approach consume 23% less dynamic power than the base circuitry but sleepy\_keeper approach results in 14% more dynamic power

Results for base logic element 4-bit adder

| 90nm                      | Static power, W | Dynamic<br>power, W | Delay, s | Area  |

|---------------------------|-----------------|---------------------|----------|-------|

| Stack                     | 196X            | 0,8X                | 2.8X     | 1.35X |

| Sleep                     | 199X            | 1X                  | 1.2X     | 1.35X |

| Sleep (multi-Vth)         | 4044X           | 1X                  | 1.3X     | 1.35X |

| Sleepy Stack              | 139X            | 0,9X                | 2.4X     | 2.87X |

| Sleepy Stack (multi-Vth)  | 199X            | 1X                  | 2.4X     | 2.87X |

| Sleepy Keeper             | 40X             | 1,1X                | 1.2X     | 1.93X |

| Sleepy Keeper (multi-Vth) | 41X             | 1,1X                | 1.2X     | 1.93X |

| Dual sleep                | 145X            | 1X                  | 1.2X     | ?     |

| Dual sleep (multi-Vth)    | 775X            | 1X                  | 1.2X     | ?     |

### **Conclusions of modeling**

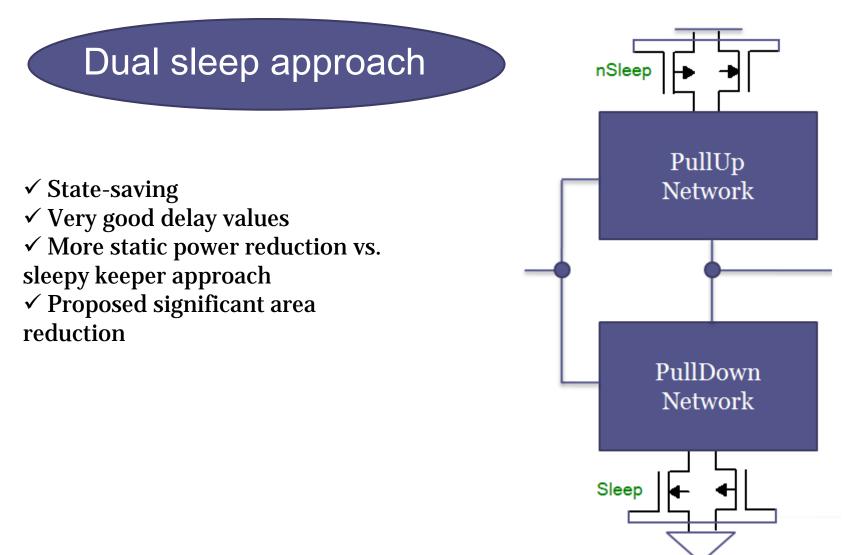

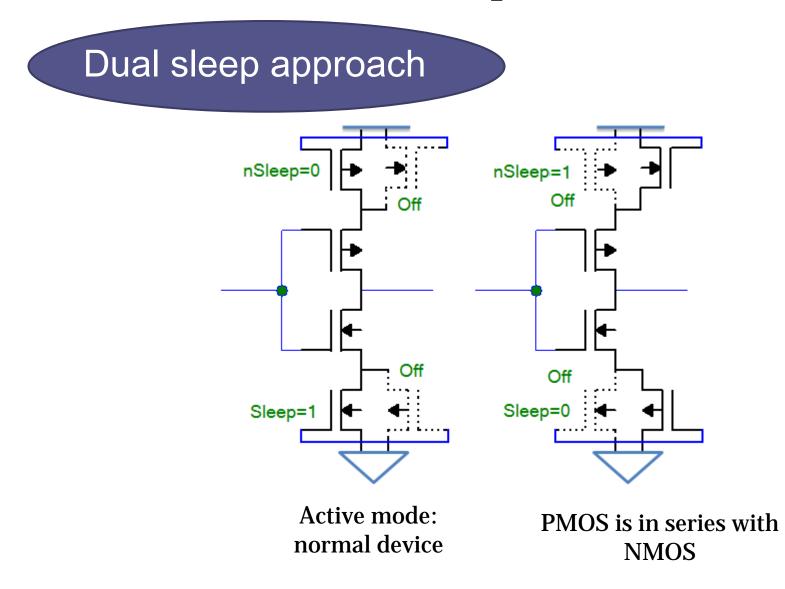

- The novel dual sleep approach shows the best performance among the state-saving techniques

- Dual sleep approach also shows the delay values compared to the delay of sleepy\_keeper approach and they are minimal for all state-saving techniques

- The minimal area overhead vs. sleepy\_keeper approach in the case of many of the sequentially connected homogeneous circuits

- According to the analysis it's better for designers to use sleepy\_keeper and dual sleep approaches

•Previous approaches are also effective in some cases, based upon the technology and design criteria

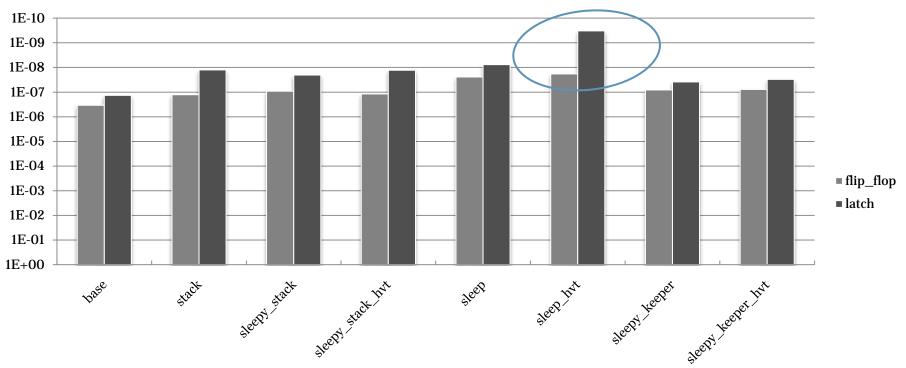

Static power consumption of flip-flop and latch realization for 90 nm technology, W

$\checkmark$  Stack and sleepy\_stack approaches using Multi  $V_{th}$  have 1 order of magnitude leakage reduction over the base case

✓ Sleepy\_keeper approach results only 0.5 order of magnitude leakage reduction

✓ State-destructive sleep approach leads to the highest reduction using transistors with high threshold voltage: 2.1 order of magnitude

Delay of flip-flop and latch realization for 90 nm technology, s

✓ Sleepy\_stack and stack approaches have great delay penalty again (up to 2.7X over base case for stack approach)

✓ Sleep and sleepy\_keeper approaches results in best delay for latch over all methods (1.4X penalty for sleepy\_keeper approach for latch )

Dynamic power consumption of flip-flop and latch realization for 90 nm technology, W

✓ Sleepy\_keeper approach consume 44% more dynamic power than the base circuitry for flip\_flop

#### **Conclusions of modeling**

- All these methods of static power reduction can be applied to the trigger circuits

- They are not so efficient, as if we'll use them in sequential circuits

### **Suggestions for future work**

- Analysis of usage dual sleep approach with trigger circuits (flip-flop, latch)

- Analysis of impact the threshold voltage and temperature variation on dependence of static power, dynamic power and delay using state-saving techniques

# Thank you!